Masks have always been an essential part of the lithography process in the semiconductor industry. With the smallest printed features already being subwavelength for both DUV and EUV cases at the bleeding edge, mask patterns play a more crucial role than ever. Moreover, in the case of EUV lithography, throughput is a concern, … Read More

Tag: opc

Saving Time in Physical Verification by Reusing Metadata

Physical verification is an important and necessary step in the process to tapeout an IC design, and the foundries define sign-off qualification steps for:

- Physical validation

- Circuit validation

- Reliability verification

This sounds quite reasonable until you actually go through the steps only to discover that some of the … Read More

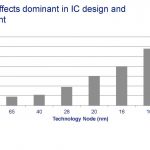

Noise, The Need for Speed, and Machine Learning

Technology trends make the concerns with electronic noise a primary constraint that impacts many mainstream products, driving the need for “Design-for-Noise” practices. That is, scaling, and the associated reduction in the device operating voltage and current, in effect magnifies the relative importance of non-scalable… Read More

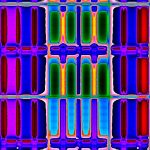

SPIE 2017 ASML and Cadence EUV impact on place and route

As feature sizes have shrunk, the semiconductor industry has moved from simple, single-exposure lithography solutions to increasingly complex resolution-enhancement techniques and multi-patterning. Where the design on a mask once matched the image that would be produced on the wafer, today the mask and resulting image … Read More

Resolution Enhancement Technology – the key to Moore’s Law

The ability to extend photolithography utilizing 193i light sources to current process nodes is truly the key technical achievement that has enabled Moore’s Law to continue. The interplay between the exposure equipment, the materials – especially, resists and related coatings – and the fundamental principles… Read More

PDK Generation Needs Paradigm Shift

For any semiconductor technology node to be adopted in actual semiconductor designs, the very first step is to have a Process Design Kit (PDK) developed for that particular technology node and qualified through several design tools used in the design flow. The development of PDK has not been easy; it’s a tedious, time consuming,… Read More

The Matrix, your ultimate OPC

One of the many consequences of shrinking process nodes is that traditional OPC can no longer achieve good pattern fidelity with reasonable turn-around-time. But there is a solution; we made it ourselves and call it matrix OPC.

First, let’s explore the problems with traditional optical proximity correction (OPC) when applied… Read More

One SPIE session not to miss

The time is nigh for another meeting of the practitioners of the lithographic arts, dark and otherwise, at the SPIE Advanced Lithography symposium.

I love this conference for the engagement you see, both in the sessions and in the hallways. People actually meet and talk and argue. There’s always interesting gossip, exciting technologies,… Read More

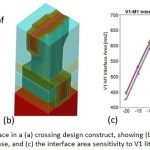

Cutting the Key to 14nm Lithography

It appears that immersion lithography is now the plan of record for manufacturing ICs at 14nm. How is it possible to use 193nm wavelength light at 14nm? How can we provide the process window to pattern the such tight pitches? The secret lies in computational lithography. For 20nm, the two key innovations in computational lithography… Read More

Magic? No! It’s Computational Lithography

The industry plans to use 193nm light at the 20nm, 14nm, and 10nm nodes. Amazing, no? There is no magic wand; scientists have been hard at work developing computational lithography techniques that can pull one more rabbit out of the optical lithography hat.

Tortured metaphors aside, the goal for the post-tapeout flow is the same… Read More