Automotive applications are one of the hottest domains today in semiconductor design. We’re bombarded daily with articles on new hybrids, electric cars, ADAS and autonomous cars, trucks and busses. All of these applications are certainly amazing, but the devices that make them work still have to deal with the same old challenges,… Read More

Tag: noise

A Complete Simulation Platform for Mobile Systems

If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More

ANSYS Enters the League of 10nm Designs with TSMC

The way we are seeing technology progression these days is unprecedented. It’s just about six months ago, I had written about the intense collaboration between ANSYSand TSMCon the 16nm FinFET based design flow and TSMC certifying ANSYS tools for TSMC 16nm FF+ technology and also conferring ANSYS with “Partner of the Year” award.… Read More

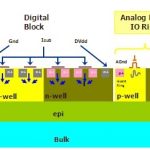

Analyze Substrate Noise in SoC Design?

Often substrate noise analysis takes place when everything is there on the chip, but that stage comes near the tape-out which is too late to make major changes in architecture, placement, introducing noise protection circuitry for the victims and so on. It was okay when there used to be very little analog content on the chip. But … Read More

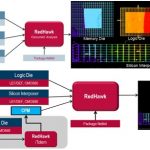

Solution for PI, TI & SI Issues in 3D-ICs

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

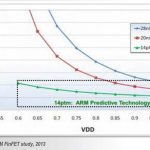

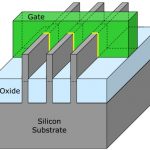

FinFET Design for Power, Noise and Reliability

IC designers have been running analysis tools for power, noise and reliability for many years now, so what is new when you start using FinFET transistors instead of planar transistors? Calvin Chow from ANSYS (Apache Design) presented on this topic earlier in the summer through a 33 minutewebinar that has been archived. There is… Read More

Intel & Ansys Enable 14nm Chip Production

In the semiconductor industry, it feels great to hear about the process technology shrinking to lower nodes along with innovative transistor structures that offer major gains in PPA (Power, Performance and Area). However, it requires huge investment of capital, time and effort from foundries to conceptualize, prototype and… Read More

IC Power Noise Reliability for FinFET Designs

Reliability for ICs is a big deal because the last thing that you want to do is ship a new part only to find out later in the field that there are failures not being caught by testing. I’ve already had two consumer products fail this year because of probable reliability issues: My MacBook Pro with 16GB of RAM started rebooting caused… Read More

IC/Package/Board – Power, Noise and Reliability from ANSYS (Apache DA) at DAC

ANSYS acquired Apache Design Automation back in June 2011and three years later the name “Apache” is being subdued in favor of using just ANSYS. One thing that I noticed right away was a DACfocus on having actual ANSYS customers talk about their hands-on experience using the EDA tools. The following seven customers… Read More

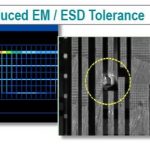

Xilinx & Apache Team up for FPGA Reliability at 20nm

In this age of SoCs with hundreds of IPs from different sources integrated together and working at high operating frequencies, FPGA designers are hard pressed keeping up the chip reliability from issues arising out of excessive static & dynamic IR drop, power & ground noise, electro migration and so on. While the IPs are… Read More