I’ll never forget debugging my first DRAM chip at Intel, peering into a microscope and watching the aluminum interconnect actually bubble and dissolve as the voltage was increased, revealing the destructive effects of Electromigration (EM) failure. That was back in 1980 using 6 um, single level metal technology, so imagine… Read More

Tag: mentor

Place & Route with FinFETs and Double Patterning

Place & route in the 16/14nm era requires a new approach since it is significantly more complex. Of course, every process generation is more complex than the one before and the designs are bigger. But modern processes have new problems. The two biggest changes are FinFETs and double patterning.

FinFETs, as I assume you know,… Read More

Mentor at TSMC OIP, 16nm, and 10nm

On Tuesday, September 30, TSMC hosts another Open Innovation Platform Ecosystem forum at the San Jose Convention Center. Have you registered? This year includes 30 technical sessions from TSMC’s ecosystem partners, divided into three separate tracks. I’ll be hanging out in the EDA track, listening to various takes on 16nm FinFET… Read More

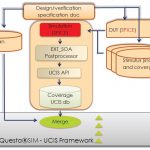

Coverage Driven Verification for Analog?

We know there is a big divide between analog and digital design methodologies, level of automation, validation and verification processes, yet they cannot stay without each other because any complete system on a chip (SoC) demands them to be together. And therefore, there are different methodologies on the floor to combine analog… Read More

Transceiver Verification of a 20nm Altera FPGA Device

FPGA devices are a great way to drive silicon technology development because they contain both digital and analog IP, along with sophisticated IO cells. The highest performance IOs are transceivers, and Altera has recently designed the Arria 10 device family to include up to 96 transceivers, using a 20nm technology that can achieve… Read More

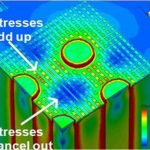

Managing Stress in 3D

A new publication on mechanical stress in integrated circuits, co-edited by Valeriy Sukharev, Principal Engineer for Calibre R&D at Mentor Graphics, has just been released by AIP Publishing. “Stress-Induced Phenomena and Reliability in 3D Microelectronics” includes 14 key papers from four international workshops … Read More

Improving Complex System Design

Next week Mike Jensen of Mentor will present a webinar Improving Complex System Design Reliability and Robustness. The webinar will be presented live twice and presumably available for replay soon after, as is usually the case:

- September 4th 6.00-6.45am pacific (9pm in Asia, 3pm in most of Europe)

- September 4th 10.00-10.45am

Mentor: It’s All About Cars

Mentor’s results came out last week. They were good. Wally opened the call:Thanks. Once again results for Mentor Graphics in the quarter exceeded our guidance. Revenue of $260.2 million and non-GAAP earnings per share of $0.23, were ahead of our guidance of $250 million and $0.15 earnings per share. Strength in bookings… Read More

Analog Model Equivalence Checking Accelerates SoC Verification

In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

Layout-aware Diagnosis

Traditional test methodologies have been based on the functional model, that is to say the netlist. The most well-known is probably the stuck-at model which grades a sequence of test vectors by whether they would have managed to notice the difference between a fully functional design and one where one of the signals was permanently… Read More