As we left an exciting year 2014 which is poised to record 7+ % increase in semiconductor revenue (~ $338 B) compared to 2013 (~ $315 B) and entered into another promising year 2015 for semiconductors, I looked back over the year bygone and collected inferences from some of the major important events which clearly convey how 2015 can… Read More

Tag: mentor

Results of TSMC’s ECO Fill Flow

By Jeff Wilson, Mentor Graphics and Anderson Chiu, TSMC

At this year’s TSMC Open Innovation Platform® (OIP) Ecosystem Forum, Mentor Graphics and TSMC co-presented some results of the ECO Fill flow developed for TSMC customers working at advanced nodes. Here is a summary of the presentation. (TSMC customers can access the presentation… Read More

Virtual Emulation Extends Debugging Over Physical

Amid burgeoning complexity of SoC verification with ever increasing hardware, software and firmware content, verification engineers are hard pressed with learning multiple tools, technologies and methodologies and still completing SoC verification with full accuracy in time. The complexity, size and diversity of SoC … Read More

HLS – Major Improvement through Generations

I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More

Predicting Component Temperature Early in Design

In today’s electronics with multiple functions working together, heat generation is on the rise; sometimes it becomes intolerable. In fact components running at different temperatures can cause timing issues, and very high temperatures can lead to operational issues such as latch-up. An electronic system can contain chips,… Read More

Coverage Driven Analog Verification

Ad hoc digital design verification approaches ran out of steam at least a decade ago when designs got intractably large to make it feasible to keep track of everything with pen and paper and excel. But analog design has remained largely ad hoc to this day. The designer runs spice, looks at the waveforms that come out and decide whether… Read More

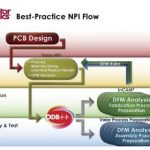

Mentor Aims to Improve Yield and Production Ramp for PCBs

Getting a printed circuit board from design and into production presents one of the biggest challenges in successfully launching a product. The designer’s job is to anticipate issues that can adversely affect PCB fabrication and assembly. Design rules and component libraries go part of the way, but there is a thicket of things… Read More

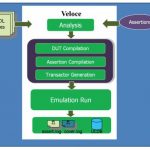

Improving Verification by Combining Emulation with ABV

Chip deadlines and the time to achieve sufficient verification coverage run continuously in a tight loop like a dog chasing its tail. Naturally it is exciting when innovative technologies can be combined so that verification can gain an advantage. Software based design simulators have been the mainstay of verification methodologies.… Read More

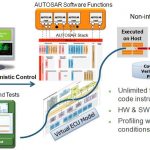

Virtual Platform Powers AUTOSAR Software Development

As a significant part of our life is spent in travelling, it’s natural that automotive sector continues to get traction with a significant push towards electronics and automated solutions for automobiles such as cars to provide safety, comfort and entertainment. These solutions are provided by complete systems which operate… Read More

Mentor Wins v Synopsys

Just a couple of days ago I read a curious press release.Mentor Graphics Corp. (NASDAQ: MENT), today announced that a Portland, Oregon jury delivered a verdict in favor of Mentor in a trial in which Mentor asserted infringement of one of its patents against Emulation and Verification Engineering S.A. (EVE) and Synopsys, Inc. (Nasdaq:… Read More