DAC 2013 is closing in fast now…and if you haven’t made your plans for what you want to see and do, you’d better get going! Of course, I’m happy to help you out with a few suggestions…starting with that most important objective—conference swag. Stop by the Mentor Graphics booth (#2046, for those of you who actually look at your floor… Read More

Tag: mentor graphics

IC Place and Route Perspective from Users at DAC

One of the most useful ways to learn about an EDA tool is to talk with other users that have experience with that tool. IC Place and Route tools are complex and yet necessary to implement every SoC designed today, so at DAC in just two weeks you have a chance to hear first-hand from several P&R tool users. To get a better idea about these… Read More

When installing a sink, it’s a lot faster to buy a saw

Mentor’s announcement from Design West this week pretty much signals the end of standalone ESL tools, in favor of more useful stuff. They have pulled the pieces of their Sourcery CodeBench environment along with their embedded Linux offering and their Vista virtual prototyping platform into a native embedded software development… Read More

Power integrity: ground, and other fairy tales

Ground. It’s that little downward-pointing triangle that somehow works miracles on every schematic. It looks very simple until one has to tackle modern power distribution network (PDN) design on a board with high speed and high power draw components, and you soon discover ground is a complicated fairy tale with a lot of influences.… Read More

New ways for High Frequency Analysis of IC Layouts

Amidst frequently changing requirements, time pressure and demand for high accuracy, it is imperative that EDA and design companies look at time consuming processes in the overall design flow and find alternatives without losing accuracy. High Frequency Analysis of IC designs is one such process which is traditionally based… Read More

Standard Cell Library Characterization

Standard cell library characterization has been around for decades, Synopsys has been offering Liberty NCXand Cadence has Virtuoso Foundation IP Characterization. What’s new is that Mentor Graphics acquired the Z Circuit technology for library characterization and has integrated it with the Eldo Classic circuit … Read More

SHIELDing the Android GPU developer in C

Repeat after me: SoCs are paperweights if they can’t be programmed. Succeeding with a new part today means supporting a robust developer program to attract and engage as many creatives as possible. NVIDIA has teamed up with Mentor Graphics in just such an adventure. If you read just the press release, you may have missed the real … Read More

Mentor Shines at DVCon

Mentor Graphics will be all over DVCon next week (February 25-28) at the DoubleTree hotel in San Jose.

In addition to attending all the panels, tutorials, posters, and the keynote, you can visit Mentor in booth 901 on the exhibit floor.

Here’s the lineup of Mentor-related events:… Read More

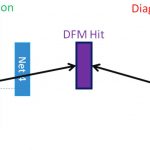

GLOBALFOUNDRIES and Mentor Develop Methods to Identify Critical Features in IC Designs

Since the beginning of the semiconductor industry, improving the rate of yield learning has been a critical factor in the success silicon manufacturing. Each fab has dedicated yield teams that look at the yield of wafers manufactured the previous day and attempt to find the root cause of any unexpected “excursions.” In earlier… Read More

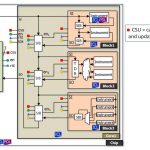

Mentor and NXP Demonstrate that IJTAG Can Reduce Test Setup Time for Complex SoCs

The creation of test patterns for mixed signal IP has been, to a large extent, a manual effort. To improve the process used to test, access, and control embedded IP, a new IEEE P1687 standard is being defined by a broad coalition of IP vendors, IP users, major ATE companies, and all three major EDA vendors. This new standard, also called… Read More