For SoCs designed for various applications such as mobile, automotive, wearable computing, gaming, virtual reality, PC, imaging, security, and IOT applications, it is incredibly important to keep area (cost) and power as low as possible. Considering the growing percentage of chip area used for memory, it makes sense to choose… Read More

Tag: memory

Arteris Unveils Solution for Heterogeneous Cache Coherent SOC’s

Designing SOC’s for markets like automotive and mobile electronics requires taking advantage of every opportunity for optimization. One way to do this is through building a cache coherent system to boost speed and reduce power. Recently, NXP decided to go about this on their automotive MCU based SOC’s by using Arteris’ just-announced… Read More

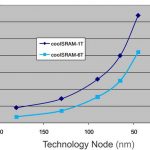

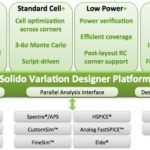

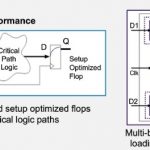

How TSMC Tackles Variation at Advanced Nodes

The design community is always hungry for high-performance, low-power, and low-cost devices. There is emergence of FinFET and FDSOI technologies at ultra-low process nodes to provide high-performance and low-power requirements at lower die-size. However, these advanced process nodes are prone to new sources of variation.… Read More

Pure-play Foundries to Prevail in Future

In a consolidating semiconductor business environment and innovation in semiconductor fabrication already scaling new heights with existing strong players, where do you think the wafer capacity should concentrate? It’s pure-play foundries or pure-play-like foundries, and those who supply high-volume common components… Read More

Advances in DDR IP Solution for High-Performance SoCs

In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More

New Sensing Scheme for OTP Memories

Last week at TSMC’s OIP symposium, Jen-Tai Hsu, Kilopass’s VP R&D, presented A New Solution to Sensing Scheme Issues Revealed.

See also Jen-Tai Hsu Joins Kilopass and Looks to the Future of Memories

He started with giving some statistics about Kilopass:

- 50+ employees

- 10X growth 2008 to 1015

- over 80 patents (including

Jen-Tai Hsu Joins Kilopass and Looks to the Future of Memories

Kilopass has a new VP of engineering, Jen-Tai Hsu. I sat down with him last week to find out where he came from and where he and Kilopass are going.

He grew up in Taiwan and went to National Taiwan University where he studied electrical engineering. Then he came to the US and went to Case Western Reserve University to get a masters degree,… Read More

Build Low Power IoT Design with Foundation IP at 40nm

In a power hungry world of semiconductor devices, multiple ways are being devised to budget power from system to transistor level. The success of IoT (Internet of Things) Edge devices specifically depend on lowest power, lowest area, optimal performance, and lowest cost. These devices need to be highly energy efficient for sustained… Read More

SmartDV at DAC and More

As we are aware about SmartDV Technologies, a fast emerging company in IP space with offices in Bangalore and San Diego, its booth in 52ndDACwas located at a prominent position in front of DAC Pavilion on the exhibits floor. So, most of the crowd coming to attend sessions in DAC Pavilion had a glimpse of SmartDV. I met Deepak Kumar Tala… Read More

The Trojan Horse Was Free Too

Timeo Danaos et dona ferentes. I fear the Greeks especially when bearing gifts. In Virgil’s Aeneid these words are spoken by the Trojan priest Laocoön warning about the wooden horse that the Greeks have offered Troy. But to no avail, Laocoön is slain by serpents and the Trojans bring the horse inside the walls of Troy. Since… Read More