There are two camps of thinking on the IoT: those who believe Bluetooth and Wi-Fi rule the edge, and those who support any of dozens of other wireless networking specifications for their various technical advantages. The ubiquity of Wi-Fi in homes helps devices connect in a few clicks – so why don’t more IoT designers use it?… Read More

Tag: low power

Tuning Analog IP for High Yield at SMIC

Analog IP is more difficult to design and optimize for a given process node compared to digital IP, so any automation for analog designers is always welcome. The engineers at SMIC in China have customers that design analog IP and often they need to know how to optimize it for a specific process, so I watched a presentation by Josh Yang,… Read More

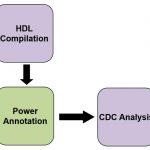

Syncing Up CDC Signals in Low Power Designs

So far in my blog series on low power we’ve looked broadly at what’s changing in the low power verification landscape and focused on a new methodology developed by Mentor Graphics and ARM called successive refinement, which is now included in the UPF standard. Power management techniques create their own brand of clock domain crossing… Read More

Optimizing power for wearables

I was at the Cadence front-end summit this week; good conference with lots of interesting information. I’ll start with a panel on optimizing power for wearables. Panelists were Anthony Hill from TI, Fred Jen from Qualcomm, Leah Clark from Broadcom and Jay Roy from Cadence. Panels are generally most entertaining when the panelists… Read More

Something Old, Something New…EDA and Verification

When I got the opportunity to blog about verification, I thought, what new and interesting things should I talk about? Having started my EDA career in 1983, I often feel like one of the “oldies” in this business…remember when a hard drive required a static strap, held a whopping 33 MB, and was the size of a brick? Perhaps they should … Read More

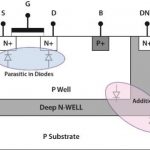

Together At Last—Combining Netlist and Layout Data for Power-Aware Verification

The market demanded that gadgets it loves become ever more conscious of their power consumption, and chip designers responded with an array of clever techniques to cut IC power use. Unsurprisingly, these new techniques added to the complexity of IC verification. When you’re verifying a design that has 100+ separate power domains,… Read More

CEVA achieves first certified Bluetooth 4.2 IP

SoC designers working on chips for the IoT and wearables now have access to cutting-edge certified Bluetooth Smart technology from CEVA. At Bluetooth ASIA in Shanghai, CEVA announced the RivieraWaves Bluetooth Smart 4.2 IP Platform has achieved full certification by the Bluetooth SIG to the Bluetooth 4.2 specification using… Read More

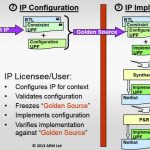

Ultra-low Power IP for Wearables

Wearables and the Internet of Things (IoT) in general are all about low power. Everyone must have read (or even experienced) the phenomenon of putting something like a Fitbit on and then after a short period leaving it in a drawer or putting it to recharge and forgetting about it for weeks. The longer devices can last the more likely… Read More

Is Low Power a Challenge? ICE-Grain Answers the Challenge

Blogs have limited wordcount so insert your own generic opening paragraph here about the importance of low power in IC design. Mention IoT and cloud datacenters for extra credit.

It is well-known that the biggest reductions in power come from changes at the architectural level. Tools and process can do some things and since they… Read More

Sensing Without (much) Power

Do you have one of those step-tracker things? They seem to be one of the earliest IoT devices that are actually selling in large quantities. Smartphones are also starting to contain this sort of sensor to provide similar functionality without requiring a separate device, as are smart-watches such as the Jumpy watch for kids on the… Read More