To wrap up Semicon West, let’s go back to Monday and the imec presentations. In fact, An Steegen’s presentation titled The Semiconductor Roadmap. She covered a lot of ground, but some of her slides contain a wealth of information. Let’s look at the options for 10nm, 7nm and a little 5nm, what imec call N10, N7 and… Read More

Tag: lithography

Cliff Hou’s DAC Keynote

Cliff Hou had two major appearances at DAC this year. He gave the opening day keynote…and he wrote the forward to Dan and my bookFabless: the Transformation of the Semiconductor Industry which about 1500 lucky people got a copy of courtesy of several companies, most notably eSilicon who sponsored the Tuesday evening post-conference… Read More

EUV Will Never Happen

I had lunch today with a guy who has to remain nameless. But he is on the edge of the semiconductor lithography thing. He told me EUV will never happen. Of course lots of people have said that. Me for one. But he said everyone knows it. The investment community, the foundries, everyone. Intel put money into ASML in the hopes that it would… Read More

New Method for Metrology with sub-10 nm Lithrography

NewPath Research will describe their new method for nanoscale carrier profiling in semiconductors on May 19[SUP]th[/SUP] at the Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC) in Saratoga Springs, NY. This new method is intended to fill the gap that has been addressed in the Roadmaps for the semiconductor… Read More

Triple Patterning

As you can’t have failed to notice by now, 28nm is the last process node that does not require double patterning. At 20nm and below, at least some layers require double patterning. The tightest spacing is typically not the transistors but the local interconnect and, sometimes, metal 1.

In the litho world they call double patterning… Read More

450mm Delayed and Other SPIE News

Last week I attended the SPIE Advanced Technology Conference. There were a lot of interesting papers and as is always the case at these conferences, there was a lot of interesting things to learn from talking to other attendees on the conference floor.

The first interesting information from the conference floor was that 450mm is… Read More

One SPIE session not to miss

The time is nigh for another meeting of the practitioners of the lithographic arts, dark and otherwise, at the SPIE Advanced Lithography symposium.

I love this conference for the engagement you see, both in the sessions and in the hallways. People actually meet and talk and argue. There’s always interesting gossip, exciting technologies,… Read More

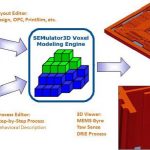

Quick MEMS Development Through Virtual Fabrication

The design and manufacture of MEMS is very different and in many ways more complex process than even the most advanced ICs. MEMS involve multiple degrees of freedom (i.e. the device to exhibit different characteristics under different physical state, motion or mechanics), making fabrication of MEMS extremely complex; and hence… Read More

Lithography: Future Technologies

The first part of Lars Liebmann’s ICCAD keynote about lithography was on the changes in lithography that have to us to where we are today. In some ways it was an explanation of why we have the odd design rules, double patterning etc that we have in 20nm and 16nm processes. The second part of his talk was a look forward to how we might… Read More

The Rosetta Stone of Lithography

At major EDA events, CEDA (the IEEE council on EDA, I guess you already know what that bit stands for) hosts a lunch and presentation for attendees and others. This week was ICCAD and the speaker was Lars Liebmann of IBM on The Escalating Design Impact of Resolution-Challenged Lithography. Lars decided to give us a whirlwind tour … Read More