Building a better mousetrap plays a key role in achieving market success in any industry. Of course, building one requires differentiating the product from the others already in the market. A differentiated product can even lead to creating demand for new products in adjacent markets. All of this is great but how do you implement… Read More

Tag: ip integration

Xilinx Moves from Internal Flow to Commercial Flow for IP Integration

I’ll never forget first learning about Xilinx when they got started back in 1984, because the concept of a Field Programmable Gate Array (FPGA) was so simple and elegant, it was rows and columns of logic gates that a designer could program to perform any logic function, then connect that logic to IO pads to drive other chips … Read More

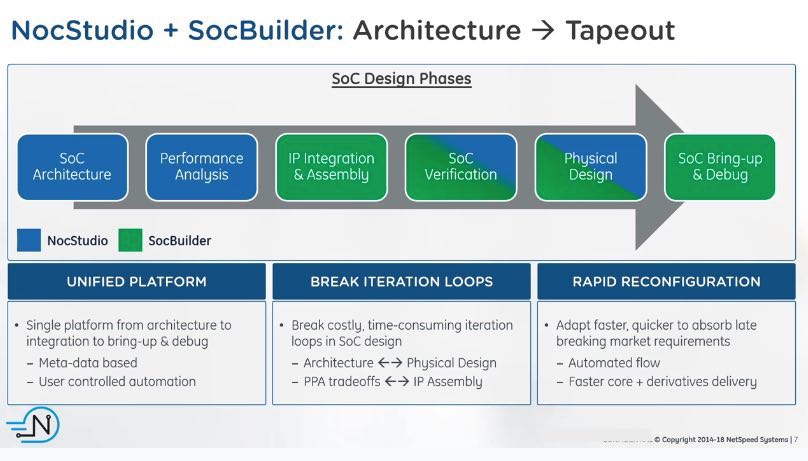

Webinar: NetSpeed is about to change the way SOCs are designed

A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning… Read More

Organizing Data is First Step in Managing AMS Designs

Efficient collaboration is essential to meeting tight chip design schedules. In analog and mixed signal (AMS) design, collaboration has many facets. Design tools are usually specific to roles, and handoffs are numerous, especially when moving a design to a foundry. … Read More

The Role of IP Selection and Integration in First-Time Silicon Success

As IP expert Eric Esteve has written, Semiconductor IP has consistently outgrown the other design enablement segments and will continue to do so. This has been my personal experience as well during my EDA and IP career so we should all know how important Semiconductor IP is. We certainly know how valuable it is with ARM valued at $32B!… Read More

A Brief History of Defacto Technologies

In early 2000s, semiconductor design at RTL level was gaining momentum. The idea was to process more design steps such as insertion of test and other design structures upfront at the RTL level. The design optimization and verification were to be done at the RTL level to reduce long iterations through gate level design because changes… Read More

SoCs in New Context Look beyond PPA

If we look back in the last century, performance and area were two main criteria for semiconductor chip design. All design tools and flows were concentrated towards optimizing those two aspects. As a result, density of chips started increasing and power became a critical factor. Now, Power, Performance and Area (PPA) are looked… Read More

Dealing with FPGA IP in all its forms

One of the recurring themes I see here in the pages of SemiWiki and elsewhere is this pitched, bordering on religious battle between Altera and Xilinx. Just because both are FPGA technologies, the tendency is to put them in the same bucket, drawing direct comparisons between them. Some folks say there is no comparison; Xilinx has… Read More

Webinar: IP integration methodology

The next Apache webinar is coming up on 21st July at 11am Pacific time on “IP integration methodology”.

This webinar will be conducted by Arvind Shanmugavel, Director Applications Engineering at Apache Design Solutions. Mr. Shanmugavel has been with Apache since 2007, supporting the RedHawk and Totem product … Read More