The release and scattering of photoelectrons and secondary electrons in EUV resists has often been glossed over in most studies in EUV lithography, despite being a fundamental factor in the image formation. Fortunately, Intel has provided us with a laboriously simulated electron release and scattering model, using the GEANT4… Read More

Tag: intel

Semiconductors Headed Toward Strong 2024

The global semiconductor market is now solidly in a turnaround. WSTS revised its data for 2Q 2023 growth over 1Q 2023 to 6.0% from 4.2% previously. 3Q 2023 was up 6.3% from 2Q 2023. With our Semiconductor Intelligence forecast of 3% growth in 4Q 2023, the year-to-year growth in 4Q 2023 will be a positive 6%. This will set the stage for… Read More

KLAC- OK quarter in ugly environment- Big China $ – Little Process $ – Legacy good

- KLA has an OK quarter in an ugly market- bouncing along bottom

- Like Lam & ASML, China was huge at 43% represents more risk

- 2/3 Foundry/logic, 1/3 memory – Process tools were weak

- No change, stable , no visibility on recovery

Quarter and guide were good in continued ugly industry

As expected KLAC reported earnings at the … Read More

IEDM 2023 is Coming in December

Anyone who has read my previous IEDM articles will know I view it as one of the best conferences on semiconductor process technology. From the tutorials, short courses and the conference papers there are so many great opportunities to keep up to date on the latest developments. The following are the conference organizers’ announcements… Read More

Podcast EP186: The History and Design Impact of Glass Substrates with Intel’s Dr. Rahul Manepalli

Dan is joined by Dr. Rahul Manepalli. Rahul is an Intel Fellow and Sr. Director of Module Engineering in the Substrate Package Technology Development Organization. Rahul and his team are responsible for developing the next generation of materials, processes and equipment for Intel’s package substrate pathfinding and development… Read More

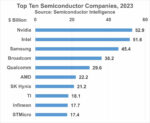

Nvidia Number One in 2023

Nvidia will likely become the largest semiconductor company for the year 2023. We at Semiconductor Intelligence (SC-IQ) estimate Nvidia’s total 2023 revenue will be about $52.9 billion, passing previous number one Intel at an estimated $51.6 billion. Nvidia’s 2023 revenue will be almost double its 2022 revenue on the strength… Read More

Podcast EP178: An Overview of Advanced Power Optimization at Synopsys with William Ruby

Dan is joined by William Ruby, director of product management for Synopsys Power Analysis products. He has extensive experience in the area of low-power IC design and design methodology, and has held senior engineering and product marketing positions with Cadence, ANSYS, Intel, and Siemens. He also has a patent in high-speed… Read More

Accellera and Clock Domain Crossing at #60DAC

Accellera sponsored a luncheon panel discussion at #60DAC, so I registered and attended to learn more about one of the newest working groups for Clock Domain Crossing (CDC). An overview of Accellera was provided by Lu Dai, then the panel discussion was moderated by Paul McLellan of Cadence, with the following panel members:

- Anupam

SEMICON West 2023 Summary – No recovery in sight – Next Year?

-SEMICON well attended but bouncing along the biz bottom

-Recovery seems at least a year away with memory even more

-AI creates hope but not impactful- Disconnect tween stocks & reality

-AMAT me too platform- Back end benefits from chiplets

SEMICON busy but subdued

SEMICON is certainly back to pre-covid levels or perhaps better.… Read More

Podcast EP169: How Are the Standards for the Terabit Era Defined?

Dan is joined by Priyank Shukla of Synopsys and Kent Lusted of Intel.

Priyank Shukla is a Sr. Staff Product Manager for the Synopsys High-Speed SerDes IP portfolio. He has broad experience in analog, mixed-signal design with strong focus on high performance compute, mobile and automotive SoCs.

Kent Lusted is a Principal Engineer… Read More