If you don’t know about Karen Bartleson, before I get into details, let me tell you that she was the President of IEEE-SA for the past 2 years and has been nominated by the IEEE Board of Directors as one of the candidates for IEEE President-Elect for 2016. The IEEE is an organization I admire as it plays a key role in advancing technology… Read More

Tag: ieee

Power Management Gets Tricky in IP Driven World

Today, an SoC can have multiple instances of an IP and also instances of many different IPs from different vendors. Every instance of an IP can work in a separate mode and requires a dedicated power arrangement which may only be formalized at the implementation stage. The power intent, if specified earlier, will need to be re-generated… Read More

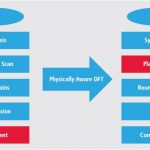

Physically Aware DFT Improves PPA

Introducing on-chip test circuitry has become a necessary criteria for an ASIC’s post manufacture testability. The test circuitry is usually referred as DFT (Design-for-Test) circuit. A typical methodology for introducing DFT circuit in a design is to replace usual flip-flops with special types of flip-flops called ‘scan… Read More

A Comprehensive Automated Assertion Based Verification

Using an assertion is a sure shot method to detect an error at its source, which may be buried deep within a design. It does not depend on a test bench or checker, and can fire automatically as soon as a violation occurs. However, writing assertions manually is very difficult and time consuming. To do so require deep design and coding… Read More

Measuring Metastability

Measuring metastability is just 50 years old this year. In 1965 my colleague Tom Chaney took a sampling ‘scope picture of an ECL flip-flop going metastable. S. Lubkin had made mention of the phenomenon over a decade before that, but at that time most engineers were unaware of the phenomenon or did not believe it actually existed. … Read More

Its a bouncing baby IEEE standard!

Pass the cigars! On November 3rd, 2014, the IEEE-SA Standards Board finally approved IEEE P1687 as a new standard. From now on, you can drop the “P” and just call it 1687, or to its friends, IJTAG. Now would be a good time to sign up for an IJTAG technical workshop.

The new IEEE 1687 Internal JTAG (IJTAG) standard is changing… Read More

SEMI Breakfast Forums: the Internet of Things

Coming up on April 10th is the SEMI Silicon Valley Breakfast Forum Internet of Things—Driving the Microelectronics Revolution. It runs from 7am to 10.45am and will be held at SEMI Headquarters which is at 3081 Zanker Road in San Jose.

Widespread adoption of the Internet of Things will take time, but the movement is advancing thanks… Read More

Grid Vision 2050 – Unified & Open Across The Globe

Whenever there is good momentum in a particular technology, IEEEtakes major initiative to standardize the procedures, formats, methods, measurements etc. involved in the technology to proliferate it for the advantage of wider community. And that becomes successful by active participation and collaboration of both producers… Read More

TSMC ♥ Synopsys (HSPICE)

In case you haven’t noticed, Synopsys has been in the press lately talking about their relationship with TSMC. Since I’m an internationally recognized industry expert they gave me a call for a briefing and I was happy to do it. Staying connected with the #1 EDA company is important and fun since I get to ask questions that most people… Read More

ICCAD at 30: Alberto Looks Back and Forward

At ICCAD earlier this week, CEDA sponsored a talk by Alberto Sangiovanni-Vincentelli looking back over the last 30 years (it is the 30th anniversary of ICCAD) and looking to the future. As is always the case in these sorts of presentations, the retrospective contained a lot more detail than the going forward part. Clayton Christensen… Read More