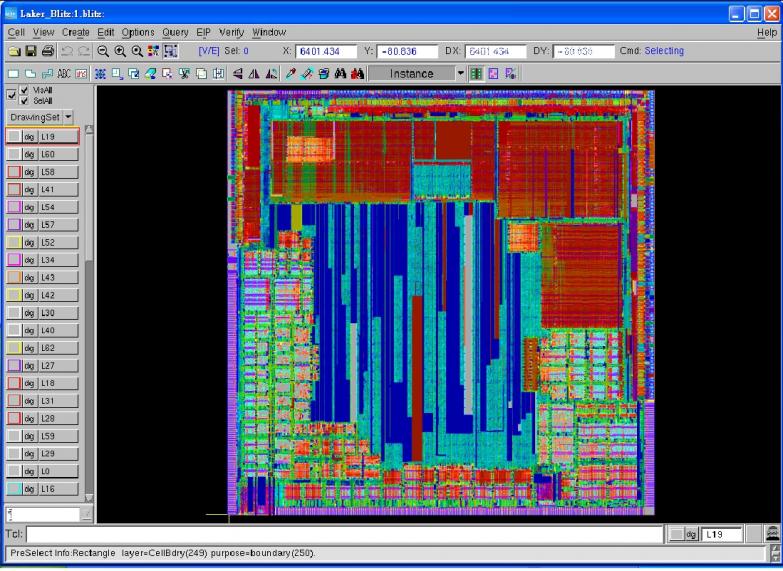

Debugging an IC design at the transistor, Gate and RTL levels is often necessary to meet timing requirements and understand analog or digital behavior, yet the process itself can be a tedious one, filled with manual steps, therefore making it an error-prone process. EDA tools have been created to help us graphically debug transistor,… Read More

Tag: ic design

Enabling 14nm FinFET Design

There’s never a dull moment in the foundry race to offer FinFET processes that enable leading-edge SoC design. Today I attended a webinar hosted by Samsung and Synopsys on how to enable 14nm FinFET design. The two speakers were Dr. Kuang-Kuo Lin from Samsung and Dr. Henry Sheng from Synopsys.

Dr. Kuang-Kuo Lin, Samsung

Dr.… Read More

Bringing Sanity to Analog IC Design Verification

Two weeks ago I blogged about analog verification and it started a discussion with 16 comments, so l’ve found that our readers have an interest in this topic. For decades now the Digital IC design community has used and benefited from regression testing as a way to measure both design quality and progress, ensuring that first… Read More

IC Place and Route Perspective from Users at DAC

One of the most useful ways to learn about an EDA tool is to talk with other users that have experience with that tool. IC Place and Route tools are complex and yet necessary to implement every SoC designed today, so at DAC in just two weeks you have a chance to hear first-hand from several P&R tool users. To get a better idea about these… Read More

RTL Restructuring

Hierarchical IC design has been around since the dawn of electronics, and every SoC design today will use hierarchy for both the physical and logical descriptions. During the physical implementation of an SoC you will likely run into EDA tool limits that require a re-structure of the hierarchy. This re-partitioning will cause… Read More

Tanner EDA Tops 1,200 Active Customers!

It is always nice to see when an EDA company grows organically, versus inorganically by acquiring friends and foes. It is also nice to see when an EDA company invests in the fabless semiconductor ecosystem because, as we know, we are all in this together.

Tanner EDA celebrated its 25th anniversary this year by adding 149 new customers… Read More

Multi-Voltage IC Design Flow

My new iPad lasts about 10 hours on a single charge and the A5X processor is designed with a 45nm process from Samsung. Processor chips for tablets like this use a multi-voltage IC design flow to reduce total power by:… Read More

SpringSoft Update 2012!

Little known fact, SpringSoft, Inc. is the largest supplier of EDA software in Asia with headquarters in both Hsinchu, Taiwan, and in Silicon Valley, CA. You will be hard pressed to find a company that does not use SpringSoft products and being located right down the street from the top two foundries doesn’t hurt either.

… Read More