China has always been an intriguing semiconductor puzzle that very few companies have solved and now it is much more puzzling with the current political meandering. The GlobalFoundries vision of having foundries all over the world was very appealing to me back in 2009 and even more so today. Remember, China consumes more than half… Read More

Tag: finfet

Parasitic Extraction for Advanced Node and 3D-IC Designs

Technology scaling has made positive impacts on device performance, while creating challenges on the interconnects and the fidelity of its manufactured shapes. The process dimension scaling has significantly increased metal and via resistance for advanced nodes 7nm and onward, as shown in figures 1a,1b. Similar to a fancy… Read More

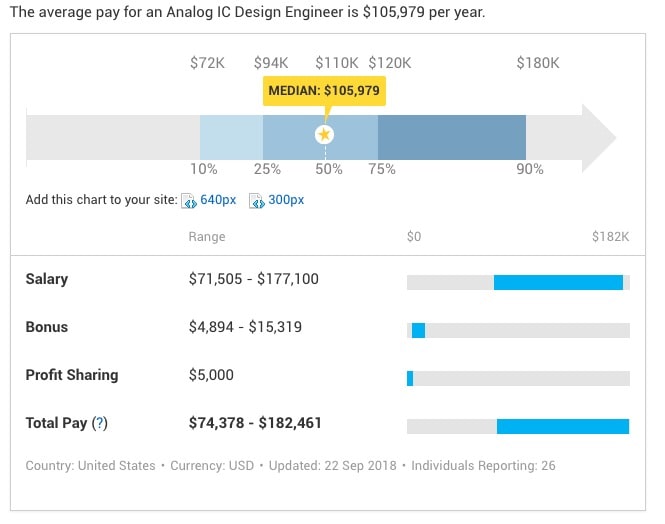

Essential Analog IP for 7nm and 5nm at TSMC OIP

When TSMC’s annual Open Innovation Platform Exposition takes place, you know it will be time to hear about designs starting on the most advanced nodes. This year we were hearing about 7nm and 5nm. These newer nodes present even more challenges than previous nodes due to many factors. Regardless of what kind of design you are undertaking… Read More

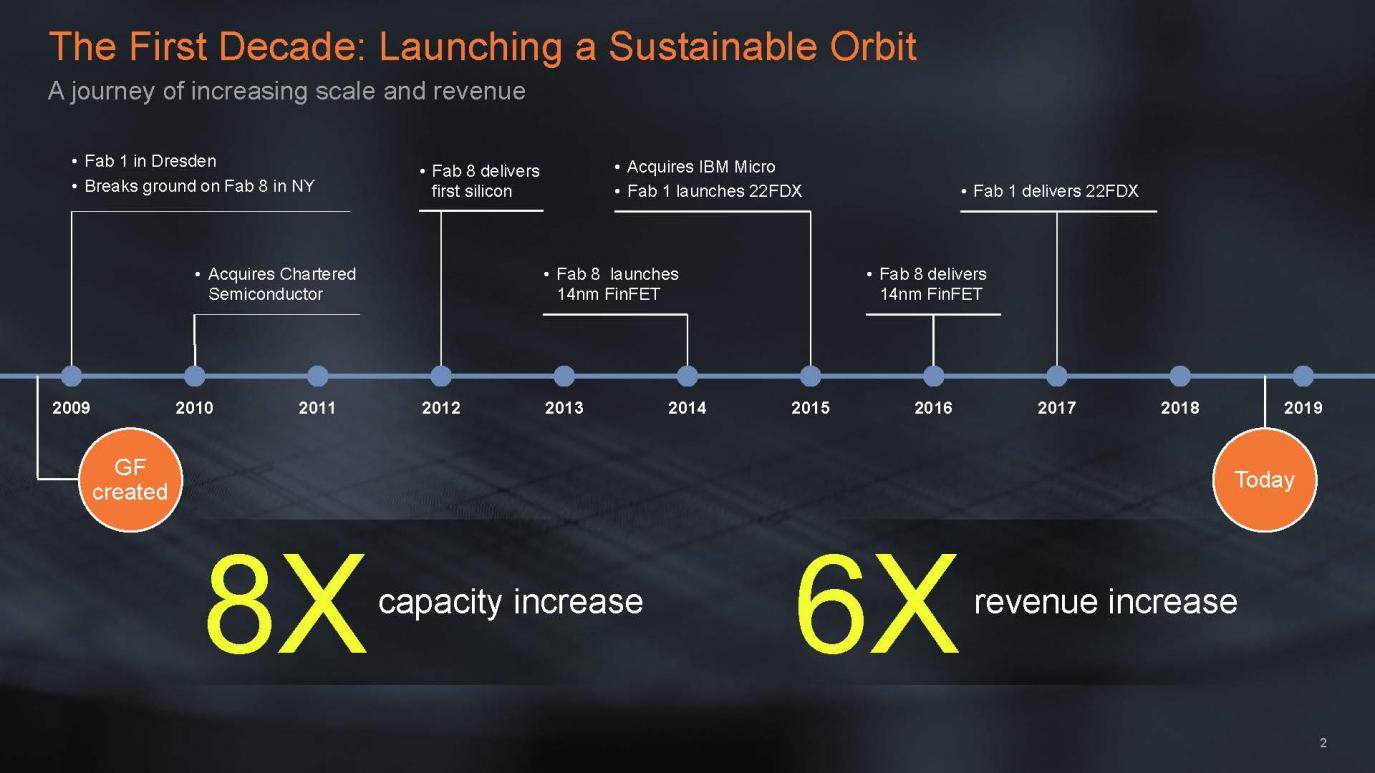

GLOBALFOUNDRIES Pivot Explained

GLOBALFOUNDRIES (GF) recently announced they were abandoning 7nm and focusing on “differentiated” foundry offerings in a move our own Dan Nenni described as a “pivot”, a description GF appears to have embraced. Last week GF held their annual Technology Conference and we got to hear more about the pivot from new CEO Tom Caulfield… Read More

Make Versus Buy for Semiconductor IP used in PVT Monitoring

As an IC designer I absolutely loved embarking on a new design project, starting with a fresh, blank slate, not having to use any legacy blocks. In the early 1980’s we really hadn’t given much thought to re-using semiconductor IP because each new project typically came with a new process node, so there was no IP even ready… Read More

Custom SoC Platform Solutions for AI Applications at the TSMC OIP

The TSMC OIP event is next week and again it is packed with a wide range of technical presentations from TSMC, top semiconductor, EDA, and IP companies, plus long time TSMC partner and ASIC provider Open-Silicon, a SiFive Company. You can see the full agenda HERE.

AI is revolutionizing and transforming virtually every industry… Read More

Optimization and Reliability for FinFET designs at #55DAC

TSMC is the leading foundry worldwide and they make a big splash each year at the DAC exhibit and conference, so I stopped by their theatre area during the presentation from IP vendor Moortec to see what’s new this year. Stephen Crosher was the presenter from Moortec and we had exchanged emails before, so this was the first time… Read More

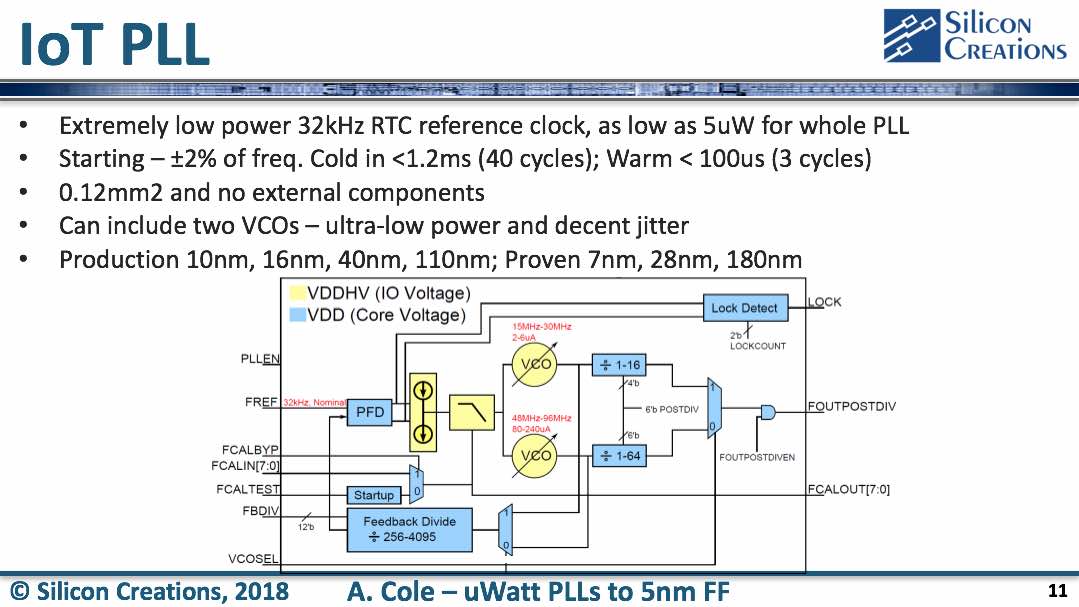

Keeping Pace With 5nm Heartbeat

A Phase-Locked Loop (PLL) gives design a heartbeat. Despite its minute footprint, it has many purposes such as being part of the clock generation circuits, on-chip digital temperature sensor, process control monitoring in the scribe-line or as baseline circuitry to facilitate an effective measurement of the design’s power… Read More

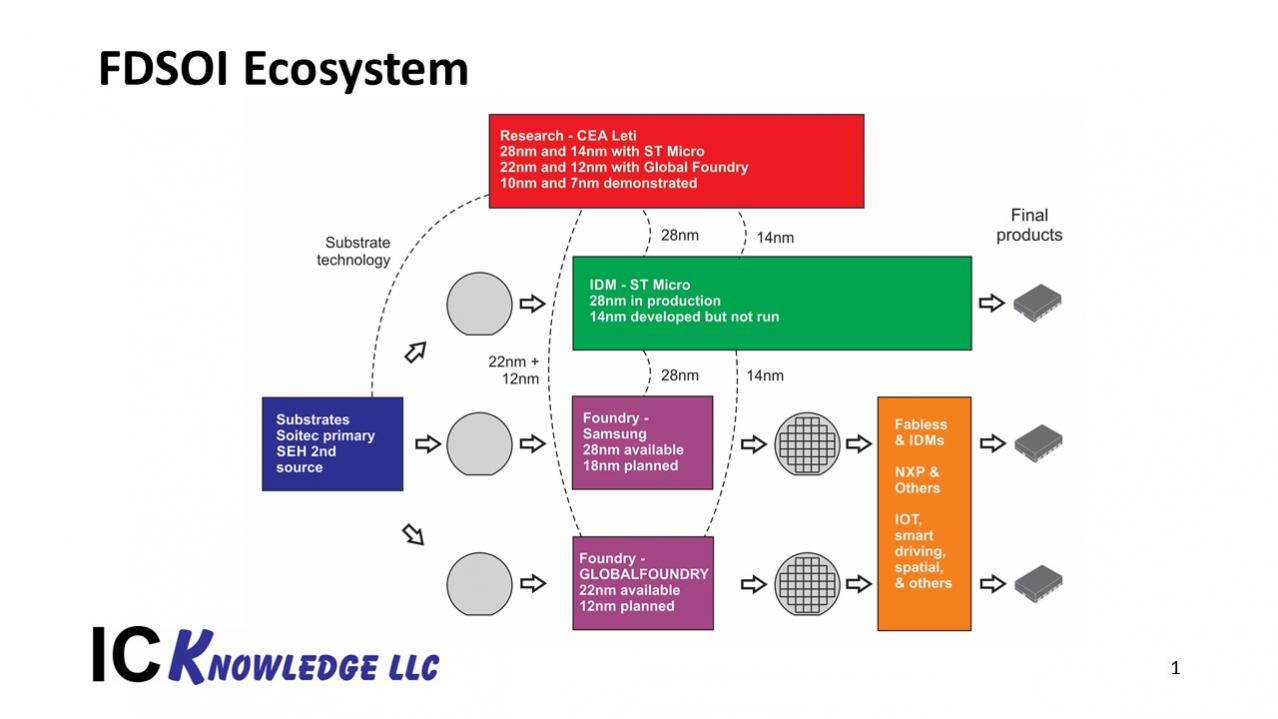

FDSOI Status and Roadmap

FDSOI is gaining traction in the market place. At their foundry forum in May, Samsung announced they have 17 FDSOI products in high volume manufacturing (you can read Tom Dilliger’s write up of the Samsung Foundry Forum here). At SEMICON West in July, GLOBALFOUNDRIES (GF) announced FDSOI design wins worth $2 billion dollars in … Read More

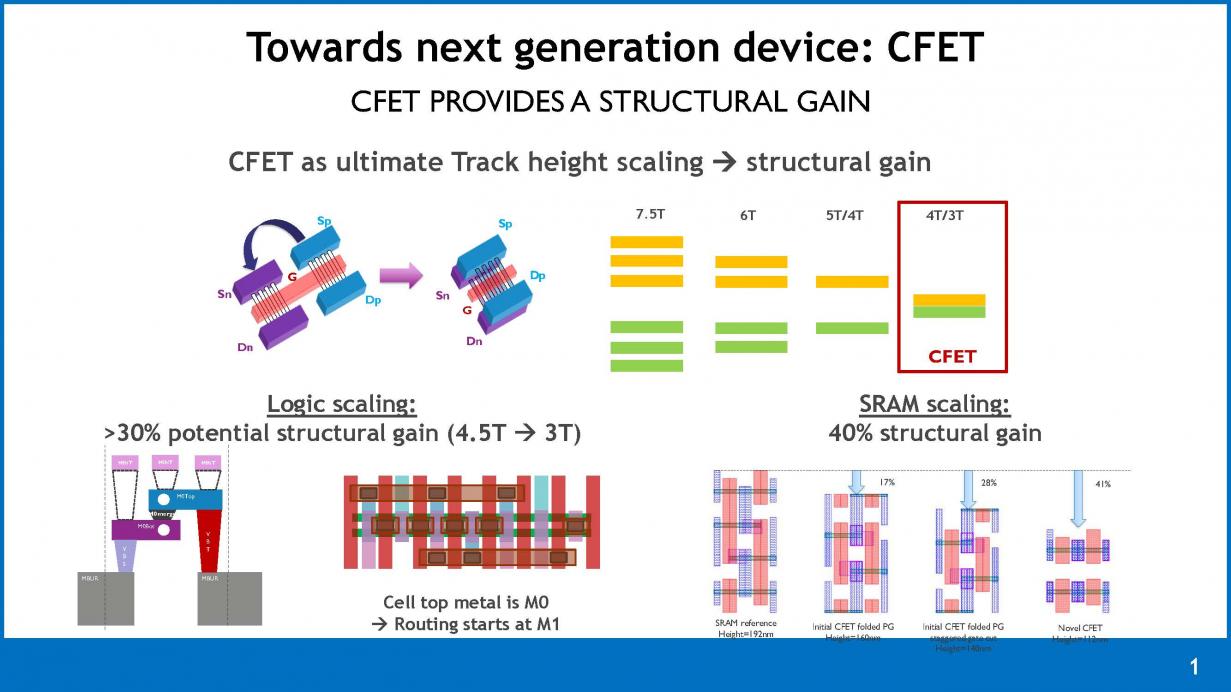

VLSIT Conference – imec on CFETs

The 2018 VLSI Technology conference was held in Hawaii in June and is one of the premier conferences covering integrated circuit process technology and circuit design. The Complementary FET (CFET) is an emerging option to continue logic scaling into the next decade. At the conference imec, GLOBALFOUNDRIES, Tokyo Electron and… Read More