In today’s SoC world where multiple analog and digital blocks along with IPs at different levels of abstractions are placed together on a single chip, debugging at all levels becomes quite difficult and clumsy. While one is working at the top level and needs to investigate a particular connection at an intermediate hierarchical… Read More

Tag: erc

Expert Tool to View and Debug Design Issues at Spice Level

Spice view of a design, block or fragment of the design is probably the lowest level of functional description of a circuit in terms of transistors, resistors, capacitors, interconnect and so on, which in several ways acts as an ultimate proof of pudding for any semiconductor design before manufacturing. However, it’s generally… Read More

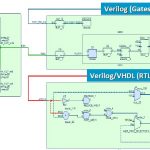

Concept Engineering Showcases Effective SoC Debugging Techniques

In a complex environment of semiconductor design where an SoC can have several millions of gates and multiple number of IPs at different levels of abstractions from different sources integrated together, it becomes really difficult to understand and debug the overall SoC design. Of course, along with the SoC integration, optimization… Read More

Ten Innovative Debugging Techniques – Pre & Post Layout

In a complex world of SoCs with multi-million gates and IPs from several heterogeneous sources, verification of a complete semiconductor design has become extremely difficult, and it’s not enough. In order to ascertain the right intent of the design throughout the design cycle, debugging at various stages of the design cycle… Read More

Customization can add extraordinary power to your tool

In EDA arena we often find companies providing customization platforms along with the tools they offer to their customers. I admire such companies because they equip the end users of a tool to extend its functionality as they like according to their environment, thus increasing the designer productivity significantly. And I’m… Read More

What Makes A Designer’s Day? A Bottleneck Solved!

In an environment of SoCs with tough targets of multiple functionalities, smallest size, lowest power and fastest performance to achieve within a limited design cycle window in order to meet the rigid time-to-market requirements, any day spent without success becomes very frustrating for a designer. Especially during tape-out… Read More

Robust Reliability Verification: Beyond Traditional Tools and Techniques

Robust Reliability Verification: Beyond Traditional Tools

by Matthew Hogan, Mentor Graphics

At all process nodes, countless hours are diligently expended to ensure that our integrated circuit (IC) designs will function in the way we intended, can be manufactured with satisfactory yields, and are delivered in a timely fashion… Read More

Design-to-Silicon Platform Workshops!

Have you seen the latest design rule manuals? At 28nm and 20nm design sign-off is no longer just DRC and LVS. These basic components of physical verification are being augmented by an expansive set of yield analysis and critical feature identification capabilities, as well as layout enhancements, printability, and performance… Read More

Aug 25th in Fremont, CA – Hands on Calibre workshop: DRC, LVS, xRC, ERC, DFM

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

DRC Wiki

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

Who Needs a 3D Field Solver for IC Design?

Prevention is Better… Read More

New ERC Tools Catch Design Errors

A growing number of reports highlight a class of design errors that is difficult to check using more traditional methods, and can potentially affect a wide range of IC designs, especially where high reliability is a must.By Matthew Hogan

Today’s IC designs are complex. They contain vast arrays of features and functionality in … Read More