Mentor has a webinar on Model Driven Development (MDD) for Systems Engineering, presented by Bill Chown. It is actually the first of 15 webinars. This first one is just over 30 minutes long and I assume the others will be too. The webinar focuses on embedded system development, which historically has largely been validated using… Read More

Tag: eda

CDNLive Call For Papers

The Silicon Valley CDNLive, the Cadence user conference, will be on March 12-13th 2013 in Santa Clara. But the heart of CDNLive are customer presentations and the call for papers is now open. The deadline is December 4th (at 5pm PST for people who really like to come down to the wire). At this point only an abstract is required.

There… Read More

The Auto Industry Speaks @ Renesas DevCon

This year’s Renesas DevCon in Orange County, CA kicked off yesterday with an impressive lineup of speakers, record attendance, and an increased focus on automotive.

“TheAuto Industry Speaks,” an Expert Panel organized by Martin Bakerof Renesas, featured:

- Yoichi Yano, RenesasExecutive VP and Member of the Board, who early

Power and Reliability Challenges

Last week I attended the Ansys/Apache seminars on “Dimensions of Electronic Design.” The two big challenges as we go down to 28nm and 20nm and below are keeping power manageable and keeping reliability up.

The big challenge with power is that we can put so much stuff on a die and clock it so fast that the power is exceeding… Read More

A Brief History of Aldec

Dr. Stanley Hyduke founded Aldecin 1984 and their first product was delivered in 1985, named SUSIE (Standard Universal Simulator for Improved Engineering), a gate-level, DOS-based simulator. The SUSIE simulator was priced lower than other EDA vendor tools from the big three: Daisy, Mentor and Valid (aka DMV). Aldec maintains… Read More

DAC: It’s the Last Week for Many Submissions

The deadline is coming up at the end of next week (technically on Monday October 29th for those of you who like real brinkmanship) for several aspects of DAC (not submission of papers for the conference itself) but most of the less academic-oriented things.

Proposals for:

- Special Sessions

- Tutorials

- Panel sessions (in the conference

Virtuoso Has Twins

Cadence has apparently announced that going forward the Virtuoso environment is going to be split into two and offered as two separate code-streams, the current IC6.x and a new IC12.x. The idea is to introduce a new product with features that were specifically developed for new technologies such as double patterning aware layout… Read More

12m FPGA prototyping sans partitioning

FPGA-based prototyping brings SoC designers the possibility of a high-fidelity model running at near real-world speeds – at least until the RTL design gets too big, when partitioning creeps into the process and starts affecting the hoped-for results.

The average ASIC or ASSP today is on the order of 8 to 10M gates, and that includes… Read More

Current Timing Closure Techniques Can’t Scale – Requires New Solution

There’s a nice article on timing closure by Dr. Jason Xing, Vice President of Engineering at ICScape Inc. on the Chip Design website. Not familiar with ICScape? Paul McLellan called ICScape the The Biggest EDA Company You’ve Never Heard Ofand Daniel Payne did Schematic, IC Layout, Clock and Timing Closure from ICScape at… Read More

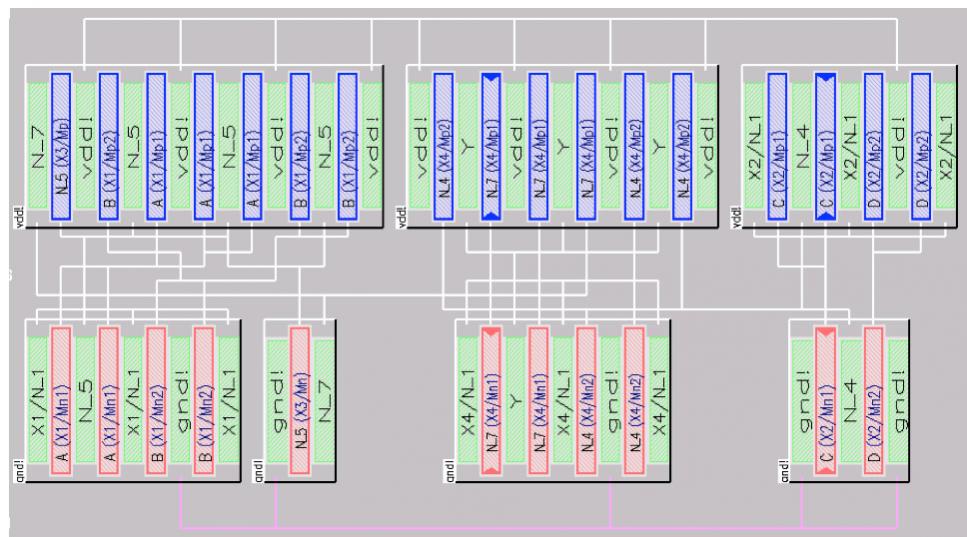

Laker3 in TSMC 20nm Reference Flow

SpringSoft, soon to be part of Synopsys but officially still a separate company for now, just announced that Laker[SUP]3[/SUP], the third generation of their layout product family, is featured in TSMC’s 20nm Custom Reference Flow.

Laker 20nm advancements include new double patterning-aware design and voltage-dependent… Read More