Wally Rhines gave the keynote at DVCon yesterday. He started out with a game of “name that graph” which was unfortunately a bit spoiled since when the names were revealed the first line was off the top of the screen. But he extrapolated several trends such as the decreasing number of fabs (the current trend is that there… Read More

Tag: eda

High and Low: High Level Synthesis and Low Power

It is so widely accepted that it is already a cliche to say that “power is the new timing.” With more and more chips, the major challenge is not so much to meet timing but to meet timing without blowing out the power budget. Otherwise, you could just crank up the clock rate.

I’m going to be lazy so you can insert your … Read More

Who Allegedly Broke Tela’s Patents: Is Samsung or Qualcomm the Real Villain?

I recently blogged about the actions filed by Tela Innovations at both the US International Trade Commission (USITC) and in federal district court. Those actions allege that five mobile phone manufacturers -HTC, LG, Motorola Mobility, Pantech, and Nokia – were importing handsets into the US which infringed on seven of… Read More

Prediction is very difficult, especially about the future

The above quote is attributed to both physicist Niels Bohr and baseball’s Yogi Berra. The statement certainly applies to predicting the semiconductor market. Semiconductors operate on physical principles. However the market for semiconductors is affected by numerous factors. The outcome of a baseball game can be determined… Read More

Cadence ♥ ClioSoft!

Taking a look at the coveted presentation slots at the CDNLive Conference next month you will see a presentation on Data Management for Mixed-Signal Designs by one of my favorite EDA companies, ClioSoft. Great software, great support, great people, and with customers that are willing to talk publicly about their tools and technology.… Read More

Why IP Must Be Defended

A few years ago I was having breakfast with Jim Hogan at our favorite place to meet in Los Gatos. I was CEO of Polyteda and Jim was Chairman so we always had plenty to talk about. This time, however, the talk had turned to protecting a company’s intellectual property (IP). Jim had brought up the topic in the context of the looming legal … Read More

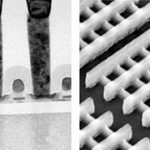

ISSCC 2013: Circuit Design Using FinFETs!

One of the privilages of blogging for SemiWiki is invitations to the top conferences around the world including the International Solid-State Circuits Conference (ISSCC) in San Francisco this week. Amazing, this conference is older than I am:

ISSCC 2013 is the 60th Conference in an incredibly long-lasting series. Following… Read More

Functional Check List in Verification

This article tries to bring out the advantages of having a functional check list. The objective is to make verification as robust as possible. Functional check list ensures the complete coverage of hardware block that is designed. This may to an extent help software developers. Creation of test plan with functional check list … Read More

Developing ARM v8 Code…Today

You are going to be developing software for an SoC that contains an ARM Cortex-A57 64-bit CPU. Or perhaps it is an SoC containing ARM’s hybrid big.LITTLE multi-core architecture that combines one or more low power cores with some high power, high performance cores to get the best of both worlds: high throughput when it is needed… Read More

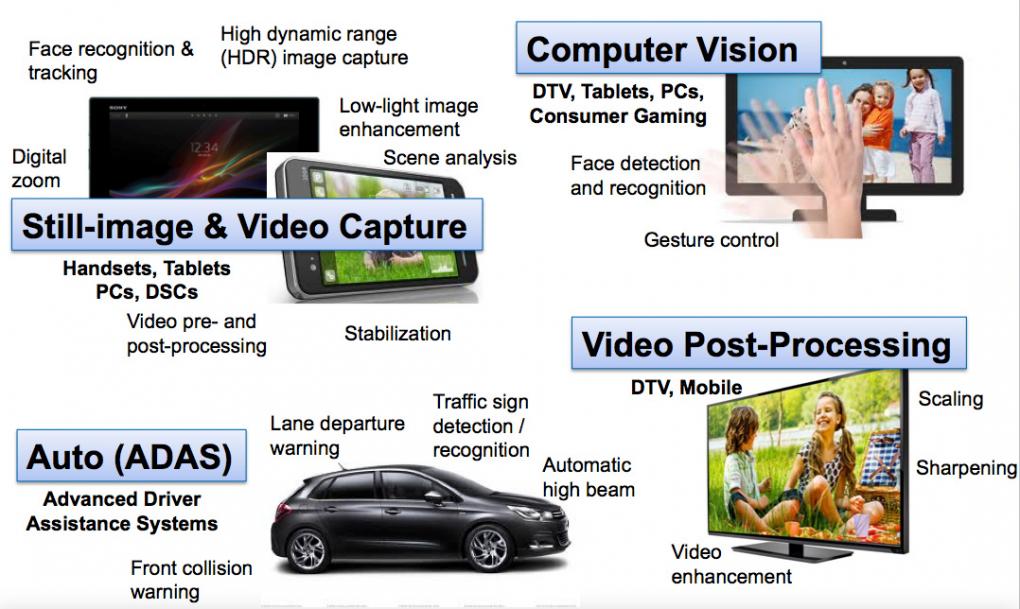

Video? Tensilica Has You Covered

Video is a huge growing area and advanced imaging applications are becoming ubiquitous. By “advanced” I mean more than just things like cameras in your smartphone. There is lots more coming, from high-dynamic range (HDR) photography, gesture recognition, more and more intelligent video in cars to keep us safe, … Read More