Clock gating is one of the most basic weapons in the armoury for reducing dynamic power on a design. All modern synthesis tools can insert clock gating cells to shut down clocking to registers when the contents of the register are not changing. The archetypal case is a register which sometimes loads a new value (when an enable signal… Read More

Tag: eda

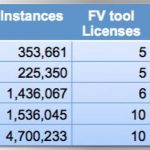

Integrating Formal Verification into Synthesis

Formal verification can be used for many things, but one is to ensure that synthesis performs correctly and that the behavior of the output netlist is the same as the behavior of the input RTL. But designs are getting very large and formal verification is a complex tool to use, especially if the design is too large for the formal tool… Read More

Cavium Adopts JasperGold Architectural Modeling

Cavium designs some very complex SoCs containing multiple ARM or MIPS cores at 32 and 64 bit. This complexity leads to major challenges in validating the overall chip architecture to ensure that their designs will meet the requirements of their customers once they are completed, with performance as high as 100Gbps.

Cavium have… Read More

SoC Derivatives Made Easier

Almost no design these days is created from scratch. Typical designs can contain 500 or more IP blocks. But there is still a big difference between the first design for a new system or platform, and later designs which can be extensively based on the old design. These are known as derivatives and should be much easier to design since… Read More

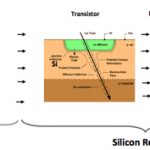

We Live on a Radioactive Planet

Often as we move down the process node treadmill, new challenges appear that we didn’t really have to worry about before. Often, these challenges require addressing at a number of different levels: the process, the cell libraries, the design, the EDA tools that we use.

One well known example is the problem of metal migration.… Read More

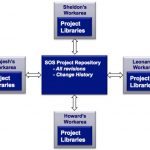

Modern Data Management

Most mixed-signal design teams don’t use data management. Well, that’s not entirely true, everyone has to do data management of some sort, it is just that it is often very ad hoc, often done by some vaguely systematic way of doing file naming, using email to keep track of changes, no access control and so on. This leads… Read More

Wally Rhines: Name That Graph!

Wally Rhines gave the keynote at DVCon yesterday. He started out with a game of “name that graph” which was unfortunately a bit spoiled since when the names were revealed the first line was off the top of the screen. But he extrapolated several trends such as the decreasing number of fabs (the current trend is that there… Read More

High and Low: High Level Synthesis and Low Power

It is so widely accepted that it is already a cliche to say that “power is the new timing.” With more and more chips, the major challenge is not so much to meet timing but to meet timing without blowing out the power budget. Otherwise, you could just crank up the clock rate.

I’m going to be lazy so you can insert your … Read More

Who Allegedly Broke Tela’s Patents: Is Samsung or Qualcomm the Real Villain?

I recently blogged about the actions filed by Tela Innovations at both the US International Trade Commission (USITC) and in federal district court. Those actions allege that five mobile phone manufacturers -HTC, LG, Motorola Mobility, Pantech, and Nokia – were importing handsets into the US which infringed on seven of… Read More

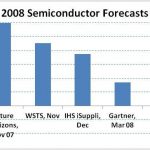

Prediction is very difficult, especially about the future

The above quote is attributed to both physicist Niels Bohr and baseball’s Yogi Berra. The statement certainly applies to predicting the semiconductor market. Semiconductors operate on physical principles. However the market for semiconductors is affected by numerous factors. The outcome of a baseball game can be determined… Read More