Back when I was a programmer at VLSI Technology in the mid-1980s, I was responsible for all the data management in the VLSI Design Tools. By responsible for, I mean that I designed the whole system and wrote all the code. Prior to the 5th release of our product, there was no data management, designers simply used filenames and it was … Read More

Tag: eda

View from the top: Brad Quinton

Many engineers dream about starting their own company some day, and today I talked with an engineer that has gone beyond the dreaming stage to actually start an EDA company and then get that company acquired. His name is Brad Quinton and the start-up was called Veridae Systems, now part of Tektronix.

Brad Quinton… Read More

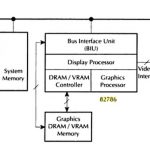

Interconnect Optimization of an SoC Architecture

My last chip design at Intel was a GPU called the 82786and the architects of the chip wrote a virtual prototype using the MAINSAIL language. By using a virtual prototype they were able to:

- Simulate bus traffic, video display and video RAM

- Determine throughput

- Measure latency

- Verify that bus priorities were working

- Optimize the

Wally Rhines, Victor Peng and Chenming Hu to Speak at Mentor User2User Conference

This year’s Mentor Graphics user group meeting, User2User, will be held at the DoubleTree by Hilton in San Jose, California on April 25, 2013. The featured keynote presenters include…

- Dr. Walden C. Rhines, CEO and Chairman of Mentor Graphics, talking about “Organizing by Design”

- Victor Peng, Senior VP, Xilinx presenting on “The

Speech Recognition : Can it be the next game changer?

The cell phone phenomena has catalyzed the technology growth and coaxed the hardware and software to work more closely. The Apple effect further directed this technology growth to focus on enhanced user experience. The emphasis has been primarily on the display and touch aspects of the designs with limited adoption on other areas.… Read More

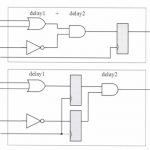

RealTime Register Retiming

I was at the EDAC CEO forecast meeting last week and one of the questions that was asked of EDAC members was “which is the hottest EDA startup?” The one with the most nominations was Oasys. So Oasys is hot.

But register retiming is hotter.

The latest announcement from Oasys this morning is that register retiming is now … Read More

A tour of today’s Mixed-Signal solution

Mixed-Signal design is one of the very initial design methodologies, pioneered by Cadence with its lead in custom design; now taking centre space in the world of SoCs. Its growth is surmountable as it finds its place in most of the high growth electronics like smart phones, automotive applications, networks and communications,… Read More

Schematic Migration Across Foundries and Processes

A dedicated schematic migration tool can save weeks of effort and allow companies to explore new foundry opportunities. Unfortunately moving analog and mixed signal design data between foundries and processes is a complex business. While engineers would rather spend their days creating new circuits, many spend time translating… Read More

Cadence IP Report Card 2013

The challenges of developing IP blocks, integrating them correctly, and hitting the power, performance, area, and time to market requirements of a mobile SoC is a growing problem. At 20nm and 14nm the probability of a chip re-spin due to an error is approaching 50% and we all know how disastrous a re-spin can be, those are not good … Read More

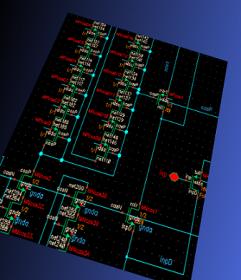

Visual Debugging at Altera on Billion-Transistor Chips

My first job out of college was doing transistor-level circuit design, so I’m always curious about how companies are doing billion-transistor chip design and debug these days at the FPGA companies.

I spoke with Yaron Kretchmer,he works at Altera and manages the engineering infrastructure group where they have a compute… Read More