Today I had the pleasure to speak with Tom Fitzpatrick, TPC Chair for the DVCon conferenceand exhibition slated for February 25-28 in the heart of Silicon Valley – San Jose. Tom lives in Massachusetts, a place where I used to live and work at Wang Labs, back in the day before the PC and WordPerfect software ended Wang’s… Read More

Tag: dvcon

DVCon is coming in February, now is the time to register early

As 2018 wraps up this month it’s time to start thinking and planning for 2019, and if you work in the Silicon Valley then you’ll want to consider adding the 31st annual DVCon event planned for February 25-28 in San Jose. Surveys have shown for some time now that verification tasks actually take up more time on a SoC project… Read More

Don’t Stand Between The Anonymous Bug and Tape-Out (Part 1 of 2)

In the EDA space, nothing seems to be more fragmented in-term of solutions than in the Design Verification (DV) ecosystem. This was my apparent impression from attending the four panel sessions plus numerous paper presentations given during DVCon 2018 held in San Jose. Both key management and technical leads from DV users community… Read More

Anirudh on Verification

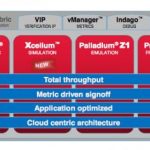

I was fortunate to have a 1-on-1 with Anirudh before he delivered the keynote at DVCon. In case you don’t know the name, Dr. Anirudh Devgan is Executive VP and GM of the Digital & Signoff Group and the System & Verification Group at Cadence. He’s on a meteoric rise in the company, not least for what he has done for Cadence’s position… Read More

Mentor gets Busy at DVCon

You’d expect Mentor to be covering a lot of bases at DVCon and you wouldn’t be wrong. They’re hosting tutorials, a lunch, papers, posters, there’s a panel and of course they’ll be on the exhibit floor. I’ll start with an important tutorial that you really should attend, Monday morning, on creating Portable Stimulus Models… Read More

VC Apps Tutorial at DVCon 2016

We might wish that all our design automation needs could be handled by pre-packaged vendor tool features available at the push of a button, but that never was and never will be the case. In the language of crass commercialism, there may be no broad market for those features, even though you consider that analysis absolutely essential.… Read More

Verdi Update and NVIDIA on Verification Compiler

Synopsys hosted a lunch session on Thursday of DVCon. Michael Sanie of Synopsys opened the session, with a look back at the last DVCon where he had talked about Verification Compiler (VC) and extending the platform to Verification Continuum, which adds emulation and FPGA-based prototyping (HAPS – there was a very cool HAPS demo… Read More

Mentor at DVCon – Visualize This

Steve Bailey entertained us during lunch on Tuesday with a talk on debug and visualization in the Mentor platform. Steve is based in Colorado, so had to spend the first part of his talk gloating about their Super Bowl win, but I guess he deserves that.

On a more technical note, he showed us a familiar survey they had completed with the… Read More

Accellera and Portable Stimulus

I’ll start with a quick note on DVCon. This seems to be gaining momentum each year. In addition to the events in the US, Europe and India, a DVCon event is now planned for China, kicking off in Shanghai in 2017. At a time when we’re all bemoaning the future of EDA and EDA conferences, DVCon is booming internationally, no doubt reflecting… Read More

Aldec reprograms HES7 for AXI4 speed

FPGA-based prototyping firms are all grappling with the problem of higher speed connectivity between a development host and their hardware. Aldec is announcing their solution at DVCon 2016, turning to an AMBA AXI4 interface bridged into a host with PCIe x8.

Faster host interfaces deliver dual benefits in FPGA-based prototyping.… Read More