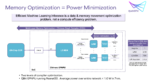

The surge in Edge AI applications has propelled the need for architectures that balance performance, power efficiency, and flexibility. Architectural choices play a pivotal role in determining the success of AI processing at the edge, with trade-offs often necessary to meet the unique demands of diverse workloads. There are… Read More

Tag: dsp

Accelerating Development for Audio and Vision AI Pipelines

I wrote previously that the debate over which CPU rules the world (Arm versus RISC-V) somewhat misses the forest for the trees in modern systems. This is nowhere more obvious that in intelligent audio and vision: smart doorbells, speakers, voice activated remotes, intelligent earbuds, automotive collision avoidance, self-parking,… Read More

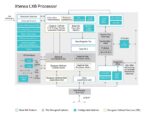

Cadence Tensilica Spins Next Upgrade to LX Architecture

When considering SoC architectures it is easy to become trapped in simple narratives. These assume the center of compute revolves around a central core or core cluster, typically Arm, more recently perhaps a RISC-V option. Throw in an accelerator or two and the rest is detail. But for today’s competitive products that view is a … Read More

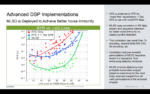

Inference Efficiency in Performance, Power, Area, Scalability

Support for AI at the edge has prompted a good deal of innovation in accelerators, initially in CNNs, evolving to DNNs and RNNs (convolutional neural nets, deep neural nets, and recurrent neural nets). Most recently, the transformer technology behind the craze in large language models is proving to have important relevance at… Read More

Next-Gen AI Engine for Intelligent Vision Applications

Artificial Intelligence (AI) has witnessed explosive growth in applications across various industries, ranging from autonomous vehicles and natural language processing to computer vision and robotics. The AI embedded semiconductor market is projected to reach $800 billion by year 2030. Compare this with just $48 billion… Read More

Tensilica Processor Cores Enable Sensor Fusion For Robust Perception

While sensor-based control and activation systems have been around for several decades, the development and integration of sensors into control systems have significantly evolved over time. Early sensor-based control systems utilized basic sensing elements like switches, potentiometers and pressure sensors and were … Read More

Driving the Future of HPC Through 224G Ethernet IP

The need for speed is a never-ending story when it comes to data communications. Currently there are a number of trends such as cloud computing, artificial intelligence, Internet of Things (IoT), multimedia applications and consumer expectations driving this demand. All of these trends are accelerating the growth in high-performance-computing… Read More

Achronix on Platform Selection for AI at the Edge

Colin Alexander ( Director of product marketing at Achronix) released a webinar recently on this topic. At only 20 minutes the webinar is an easy watch and a useful update on data traffic and implementation options. Downloads are still dominated by video (over 50% for Facebook) which now depends heavily on caching at or close to … Read More

Quadric’s Chimera GPNPU IP Blends NPU and DSP to Create a New Category of Hybrid SoC Processor

Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More

Scaling is Failing with Moore’s Law and Dennard

Looking backward and forward, the white paper from Codasip “Scaling is Failing” by Roddy Urquhart provides an interesting history of processor development since the early 1970s to the present. However it doesn’t stop there and continues to extrapolate what the chip industry has in store for the rest of this decade. For the last… Read More