The rapid growth of signal processing workloads in embedded, mobile, and edge computing systems has intensified the need for efficient, low-latency computation. Rich Fuhler’s update on the RISC-V Packed SIMD extension highlights why scalar SIMD digital signal processing (DSP) instructions are becoming a critical architectural… Read More

Tag: dsp

Inference Acceleration from the Ground Up

VSORA, a pioneering high-tech company, has engineered a novel architecture designed specifically to meet the stringent demands of AI inference—both in datacenters and at the edge. With near-theoretical performance in latency, throughput, and energy efficiency, VSORA’s architecture breaks away from legacy designs optimized… Read More

A Remote Touchscreen-like Control Experience for TVs and More

How do you control your smart TV? With a remote control of course, already quite capable since it allows voice commands to find a movie or TV show without needing all that fiddly button-based control and lookup. But there’s a range of things you can’t do that we take for granted on a tablet or phone screen. Point and click on an object,… Read More

Podcast EP291: The Journey From One Micron to Edge AI at One Nanometer with Ceva’s Moshe Sheier

Dan is joined by Moshe Sheier, Ceva’s vice president of marketing. Moshe brings with him more than 20 years of experience in the semiconductor IP and chip industries in both development and managerial roles. Prior to this position, Mr. Sheier was the director of strategic marketing at Ceva.

Dan explores the history of Ceva with … Read More

Ceva-XC21 and Ceva-XC23 DSPs: Advancing Wireless and Edge AI Processing

Ceva recently unveiled its XC21 and XC23 DSP cores, designed to revolutionize wireless communications and edge AI processing. These new offerings build upon the Ceva-XC20 architecture, delivering unmatched efficiency, scalability, and performance for 5G-Advanced, pre-6G, and smart edge applications. As demand grows … Read More

A New Class of Accelerator Debuts

I generally like to start my blogs with an application-centric viewpoint; what end-application is going to become faster, lower power or whatever because of this innovation? But sometimes an announcement defies such an easy classification because it is broadly useful. That’s the case for a recent release from Quadric, based… Read More

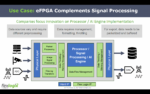

Elevating Your SoC for Reconfigurable Computing – EFLX® eFPGA and InferX™ DSP and AI

Field-Programmable Gate Arrays (FPGAs) have long been celebrated for their unmatched flexibility and programmability compared to Application-Specific Integrated Circuits (ASICs). And the introduction of Embedded FPGAs (eFPGAs) took these advantages to new heights. eFPGAs offer on-the-fly reconfiguration capabilities,… Read More

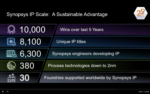

Synopsys Design IP for Modern SoCs and Multi-Die Systems

Semiconductor intellectual property (IP) plays a critical role in modern system-on-chip (SoC) designs. That’s not surprising given that modern SoCs are highly complex designs that leverage already proven building blocks such as processors, interfaces, foundational IP, on-chip bus fabrics, security IP, and others. This… Read More

A Modeling, Simulation, Exploration and Collaborative Platform to Develop Electronics and SoCs

During the GOMACTech conference held in South Carolina last week I had a Zoom call with Deepak Shankar, Founder and VP Technology at Mirabilis Design Inc. to ask questions and view a live demo of VisualSim – a modeling, simulation, exploration and collaborative platform to develop electronics and SoCs. What makes VisualSim so … Read More

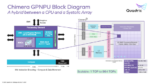

2024 Outlook with Steve Roddy of Quadric

Quadric Inc. is the leading licensor of general-purpose neural processor IP (GPNPU) that runs both machine learning inference workloads and classic DSP and control algorithms. Quadric’s unified hardware and software architecture is optimized for on-device ML inference. I have know Steve Roddy for many years, he is a high … Read More