Every SoC project that I know of wants to finish on time, under budget, and maximize profits per device. When I first started out doing DRAM design I learned that we could maximize profit by doing shrinks of existing designs, move from ceramic to plastic packages, and reduce the amount of time spent on a tester. Today, the economic … Read More

Tag: dft

SoCs in New Context Look beyond PPA – Part2

In the first part of this article, I talked about some of the key business aspects along with some technical aspects like system performance, functionality, and IP integration that drive the architecture of an SoC for its best optimization and realization in an economic sense. In this part, let’s dive into some more aspects that… Read More

Mentor and ASSET Intertech Do a DFT World Tour

The Mentor Graphics test folks and ASSET Intertech have teamed up to provide a series of free DFT seminars in the US, Europe, and Asia. The first one is in Austin, TX on February 19, 2015, and the last is in Tokyo on April 24. Hereis the full list of locations and dates.

The morning session covers IJTAG. The new IEEE 1687 Internal JTAG (IJTAG)… Read More

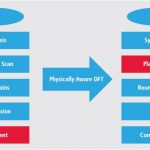

Physically Aware DFT Improves PPA

Introducing on-chip test circuitry has become a necessary criteria for an ASIC’s post manufacture testability. The test circuitry is usually referred as DFT (Design-for-Test) circuit. A typical methodology for introducing DFT circuit in a design is to replace usual flip-flops with special types of flip-flops called ‘scan… Read More

Improve Test Robustness & Coverage Early in Design

In a semiconductor design, keeping the design testable with high test coverage has always been a requirement. However with shrinking technology nodes and large, dense SoC designs and complex logic structures, while it has become mandatory to reach close to 100% test coverage, it’s extremely difficult to cope with the explosion… Read More

A Complete Scalable Solution for IP Signoff

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

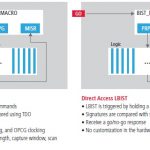

What’s next in test compression?

If you’ll be at ITC TestWeek in Seattle (Oct 20-23), here’s one event you don’t want to miss: a technology reception hosted by Mentor, with Janusz Rajski and Nilanjan Mukherjee as the featured speakers. It is free to ITC attendees and you can register here. [If for some crazy reason you haven’t registered for ITC yet, do that… Read More

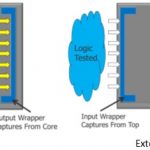

SmartScan Addresses Test Challenges of SoCs

With advancement of semiconductor technologies, ever increasing sizes of SoCs bank on higher densities of design rather than giving any leeway towards increasing chip area and package sizes; a phenomenon often overlooked. The result is – larger designs with lesser number of pins bonded out of ever shrinking package sizes;… Read More

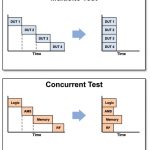

Ceaseless Field Test for Safety Critical Devices

While focus of the semiconductor industry has shifted to DACin this week and unfortunately I couldn’t attend due to some of my management exams, in my spare time I was browsing through some of the webpages of Cadenceto check their new offerings (although they have a great list of items to showcase at DAC) and to my pleasure I came across… Read More

Taming The Challenges of SoC Testability

With the advent of large SoCs in semiconductor design space, verification of SoCs has become extremely challenging; no single approach works. And when the size of an SoC can grow to billions of gates, the traditional methods of testability of chips may no longer remain viable considering the needs of large ATPG, memory footprint,… Read More