I think by now a lot has been said about the necessity of multi-patterning at advanced technology nodes with extremely low feature size such as 20nm, because lithography using 193nm wavelength of light makes printing and manufacturing of semiconductor design very difficult. The multi-patterning is a novel semiconductor manufacturing… Read More

Tag: dfm

One SPIE session not to miss

The time is nigh for another meeting of the practitioners of the lithographic arts, dark and otherwise, at the SPIE Advanced Lithography symposium.

I love this conference for the engagement you see, both in the sessions and in the hallways. People actually meet and talk and argue. There’s always interesting gossip, exciting technologies,… Read More

Signoff Summit: The Fastest Path to Design Signoff

Cadence’s Signoff Summit will be held next week, November 21 at Cadence in San Jose.

This is the first of a series of all-day Signoff Summits from Cadence that focus on the multiple facets of design signoff. This first summit will include keynote addresses plus sessions covering the multiple solution components that comprise… Read More

IROC Technologies CEO on Semiconductor Reliability

One of the best things about being part of SemiWiki is the exposure to new technologies and the people behind them. SemiWiki now works with more than 35 companies and I get to spend time with each and every one of them. Much like I do, IROC Technologies works closely with the foundries and the top semiconductor companies so it was a pleasure… Read More

Notes from Common Platform: Collaborate or Die

FinFETs are hot, carbon nanotubes are cool, and collaboration is the key to continued semiconductor scaling. These were the main messages at the 2013 Common Platform Technology Forum in Santa Clara.

The collaboration message ran through most presenations, like the afternoon talk by Subi Kengeri of GLOBALFOUNDRIES and Joe Sawicki… Read More

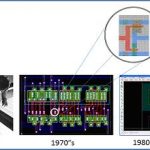

IP Scoring Using TSMC DFM Kits

Design For Manufacturing (DFM) is the art and science of making an IC design yield better in order to receive a higher ROI. Ian Smith, an AE from Mentor in the Calibre group presented a pertinent webinar, IP Scoring Using TSMC DFM Kits. I’ll provide an overview of what I learned at this webinar.… Read More

Double Patterning Exposed!

Wanna become the double patterning guru at your company? David Abercrombie, DFM Program Manager for Calibre, has written a series of articles detailing the multifaceted impacts of double patterning on advanced node design and verification. For designers struggling to understand the complexity and nuances of double patterning,… Read More

The Total ARM Platform!

In the embedded world that drives much of today’s ASIC innovation, there is no bigger name than ARM. Not to enter the ARM vs. Intel fray, but it’s no exaggeration to say that ARM’s impact on SoCs is as great as Intel’s on the PC. Few cutting edge SoCs are coming to market that do not include some sort of embedded… Read More

Design-to-Silicon Platform Workshops!

Have you seen the latest design rule manuals? At 28nm and 20nm design sign-off is no longer just DRC and LVS. These basic components of physical verification are being augmented by an expansive set of yield analysis and critical feature identification capabilities, as well as layout enhancements, printability, and performance… Read More

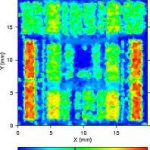

TSMC 28nm Yield Explained!

Yield, no topic is more important to the semiconductor ecosystem. After spending a significant part of my career on Design for Manufacturability (DFM) and Design for Yield (DFY), I’m seriously offended when semiconductor professionals make false and misleading statements that negatively affects the industry that … Read More