I attend a lot of events on machine learning and write about it regularly. However, I learned some exciting new information about machine learning in a very surprising place recently. Every year for the last few years I have attended the HSPICE SIG dinner hosted by Synopsys in Santa Clara. This event starts with a vendor fair featuring… Read More

Tag: design

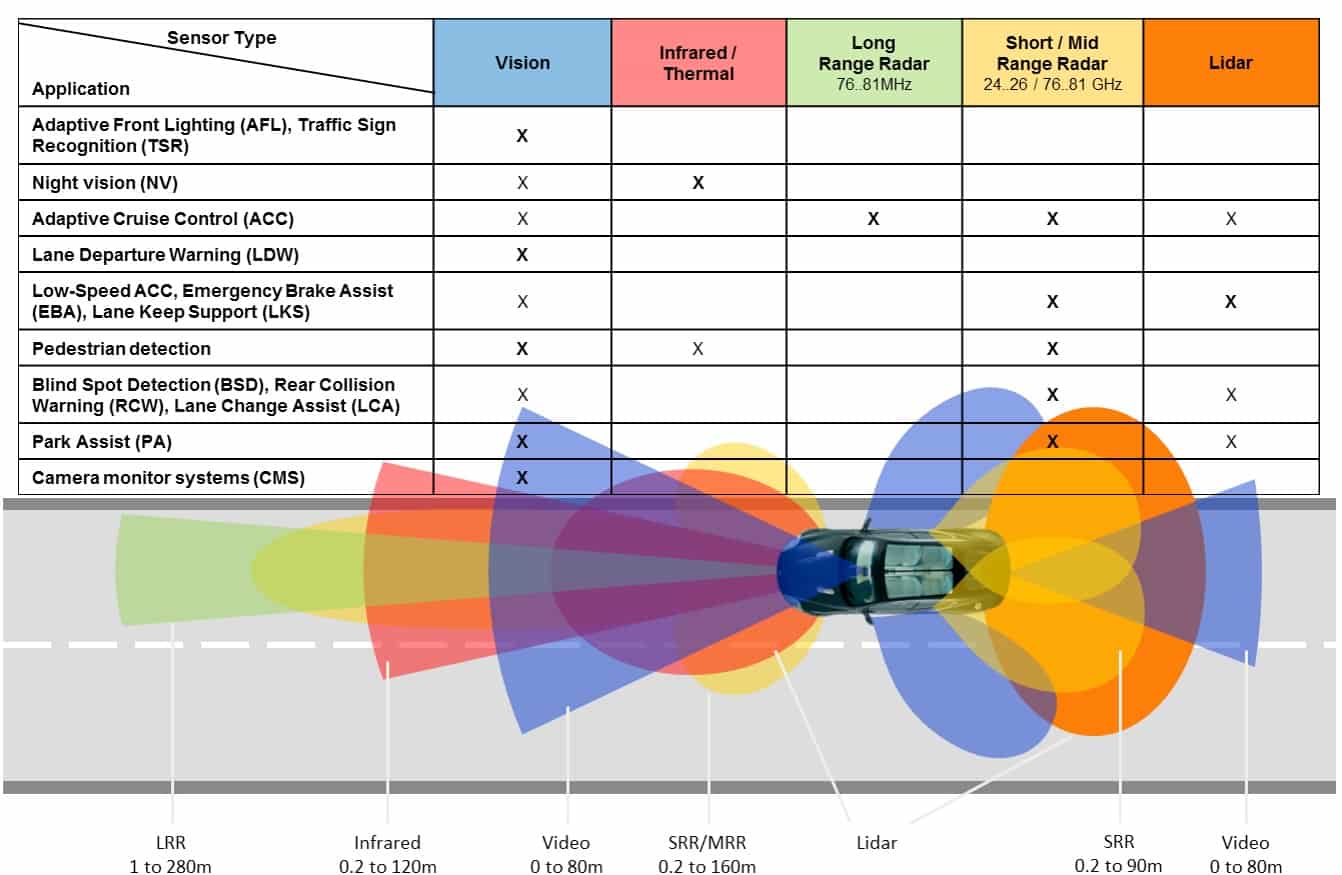

Autonomous Vehicles Upending Automotive Design Process

The automotive industry has a history of bringing about disruptive technological advances. One only needs to look at the invention of the assembly line by Henry Ford to understand the origins of this phenomenon. Today we stand on the brink of a massive change in how cars operate and consequently how they are built. A number of automotive… Read More

Using Sequential Testing to Shorten Monte Carlo Simulations

When working on an analog design, after initial design specs have been met, it is useful to determine if the design meets specs out to 3 or 4 sigma based on process variation. This can serve as a useful step before going any further. It might not be a coincidence that foundries base their Cpk on 3-sigma. To refresh, Cpk is the ratio of the… Read More

TSMC Teamwork Translates to Technical Triumph

Most people think that designing successful high speed analog circuits requires a mixture of magic, skill and lots of hard work. While this might be true, in reality it also requires a large dose of collaboration among each of the members of the design, tool and fabrication panoply. This point was recently made abundantly clear … Read More

Improved Memory Design, Characterization and Verification

My IC design career started out with DRAM design, characterization and verification back in the 1970’s, so I vividly recall how much SPICE circuit simulation was involved, and how little automation we had back in the day, so we tended to cobble together our own scripts to help automate the process a bit. With each new process… Read More

Customizable Analog IP No Longer a Pipe Dream

Configurable analog IP has traditionally been a tough nut to crack. Digital IP, of course, now provides for wide configurability for varying applications. In the same way that analog design has remained less deterministic as compared to digital design, analog IP has also tended to be less flexible. However, the tide may be turning… Read More

Why are Top Brass from NXP, Qualcomm, Skyworks Keynoting Upcoming IEEE SOI-3D-SubVt (S3S) Conference? (San Francisco, Oct.’16)

By Fred Allibert

The IEEE S3S Conference (10-13 October 2016 at the San Francisco Airport Hyatt Regency) brings together 3 key technologies that will play a major role in tomorrow’s industry: SOI, 3D integration, and Subthreshold Microelectronics. The numerous degrees of freedom they allow enable the ultra-low power operation… Read More

Semiconductor IP QA Standards Get a Boost at #53DAC

At the #53DAC earlier this month held in Austin, Texas I met up with Renee Donkers, the founder of Fractal Technologies. His company has been focused on improving the quality of semiconductor IP cells through the use of automated checking software. The highest area of growth in EDA as measured by the ESD Alliance is in the reusable… Read More

In the Valley & thinking about FD-SOI for your next chip design? Epic (and free) symposium 13 April

If you’re in the chip biz in Silicon Valley, check out the SOI Consortium FD-SOI Symposium on April 13th in San Jose. They’ve been running these things since 2009, and I have to say that this one is the most comprehensive to date. Headliners include Cisco, Sony, NXP, SigmaDesigns, ARM, Ciena plus the big FD-SOI foundries,… Read More

Positive pointers from Samsung, GF, Renesas, NXP/Freescale, ST, Soitec – so will 2016 be the year of FD-SOI?

A little over a month into 2016 and we already have a raft of FD-SOI news from Samsung, GlobalFoundries, NXP/Freescale, Renesas and more. Quite a bit of it came out of the recent SOI Consortium forum in Tokyo. Many of the presentations are now available on the SOI Consortium website (click here to see what’s there) – but keep checking… Read More