In the history of semiconductor design and manufacturing, the age-old concept of DRC rule-deck qualification for handshake between design and manufacturing still applies strongly to produce working silicon. In fact, DRC clean GDSII works as the de facto golden gate between a design and a foundry for manufacturing the chip for… Read More

Tag: dac

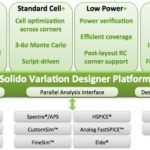

How TSMC Tackles Variation at Advanced Nodes

The design community is always hungry for high-performance, low-power, and low-cost devices. There is emergence of FinFET and FDSOI technologies at ultra-low process nodes to provide high-performance and low-power requirements at lower die-size. However, these advanced process nodes are prone to new sources of variation.… Read More

DAC 2016 – Register Now

DAC is again going to be in Austin (reason enough to go), from June 6[SUP]th[/SUP]-8[SUP]th[/SUP] for the main event. A number of events caught my eye:

- Monday AM – custom hardware for algorithmic trading. If you want to know more about FinTech (technology for finance) this could be for you

- Another Monday morning session on Linux

A Versatile Design Platform with Multi-Language APIs

In one of my whitepapers “SoCs in New Context – Look beyond PPA”, I had mentioned about several considerations which have become very important in addition to power, performance, and area (PPA) of an SoC. This whitepaper was also posted in parts as blogs on Semiwiki (links are mentioned below). Two important… Read More

Replacing the British Museum Algorithm

In principle, one way to address variation is to do simulations at lots of PVT corners. In practice, most of this simulation is wasted since it adds no new information, and even so, important corners will get missed. This is what Sifuei Ku of Microsemi calls the British Museum Algorithm. You walk everywhere. And if you don’t walk to… Read More

Moving up Verification to Scenario Driven Methodology

Verification complexity and volume has always been on the rise, taking significant amount of time, human, and compute resources. There are multiple techniques such as simulation, emulation, FPGA prototyping, formal verification, post-silicon testing, and so on which gain prominence in different situations and at different… Read More

A Complete Simulation Platform for Mobile Systems

If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More

My Tryst with Semiconductors and EDA

Yes, today I realize it feels like a tryst with semiconductors. In actual meaning; it wasn’t a love affair with semiconductors, but I must say the greatest thing it taught me about how it approaches towards perfection. And that became the guiding principle in my life; how can I do something better. Of course nothing is perfect in life… Read More

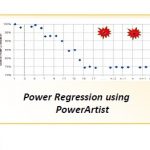

How PowerArtist Interfaces with Emulators

Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

How Emulation Enables Complex Power Intent Modeling

As the number of CPU, GPU, and IP is growing in an SoC, power management is becoming more and more a complex task in itself. A single tool or methodology may not be enough for complete power management and verification of an SoC. In an SoC, there can be multiple modes of operations involving hardware and software interactions, different… Read More