Sébastien Dauvé has been CEO of CEA-Leti since July 1, 2021. With over 20 years of experience in microelectronics and their applications—including clean mobility, future medicine, cybersecurity, and power electronics—he has played a key role in advancing digital innovation. A graduate of École Polytechnique and ISAE-SUPAERO,… Read More

Tag: cea-leti

Podcast EP331: Soitec’s Broad Impact on Quantum Computing and More with Dr. Christophe Maleville

Daniel is joined by Dr. Christophe Maleville, Chief Technology Officer and Senior Executive Vice-President of Soitec’s Innovation. He joined Soitec in 1993 and was a driving force behind the company’s joint research activities with CEA-Leti. For several years, he led new SOI process development, oversaw SOI technology transfer… Read More

CEO Interview with Sébastien Dauvé of CEA-Leti

Podcast EP209: Putting Soitec’s Innovative Substrates to Work in Mainstream Products with Dr. Christophe Maleville

Dan is joined by Dr. Christophe Maleville, chief technology officer of Soitec’s Innovation. He joined Soitec in 1993 and was a driving force behind the company’s joint research activities with CEA-Leti. For several years, he led new SOI process development, oversaw SOI technology transfer from R&D to production and managed… Read More

CEO Interview: Coby Hanoch of Weebit Nano

Coby Hanoch comes to Weebit Nano with 15 years’ experience in engineering and engineering management and 26 years’ experience in sales management and executive roles. Coby was Vice President Worldwide Sales at Verisity where he was part of the founding team and grew the company to over $100M in annual sales which facilitated its… Read More

IEDM 2019 – IBM and Leti

IBM and Leti each presented several papers at IEDM including a joint nanosheet paper. I had the opportunity to sit down with Huiming Bu, director of advanced logic & memory tech and Veeraraghavan Basker, senior engineer from IBM and then in a separate interview Francois Andrieu, head of advanced CMOS laboratory and Shay Reboh,… Read More

Semicon West 2019 – Day 2

Tuesday July 9th was the first day the show floor was open at Semicon. The following is a summary of some announcements I attended and general observations.

AMAT Announcement

My day started with an Applied Materials (AMAT) briefing for press and analysts where they announced “the most sophisticated system they have ever released”.… Read More

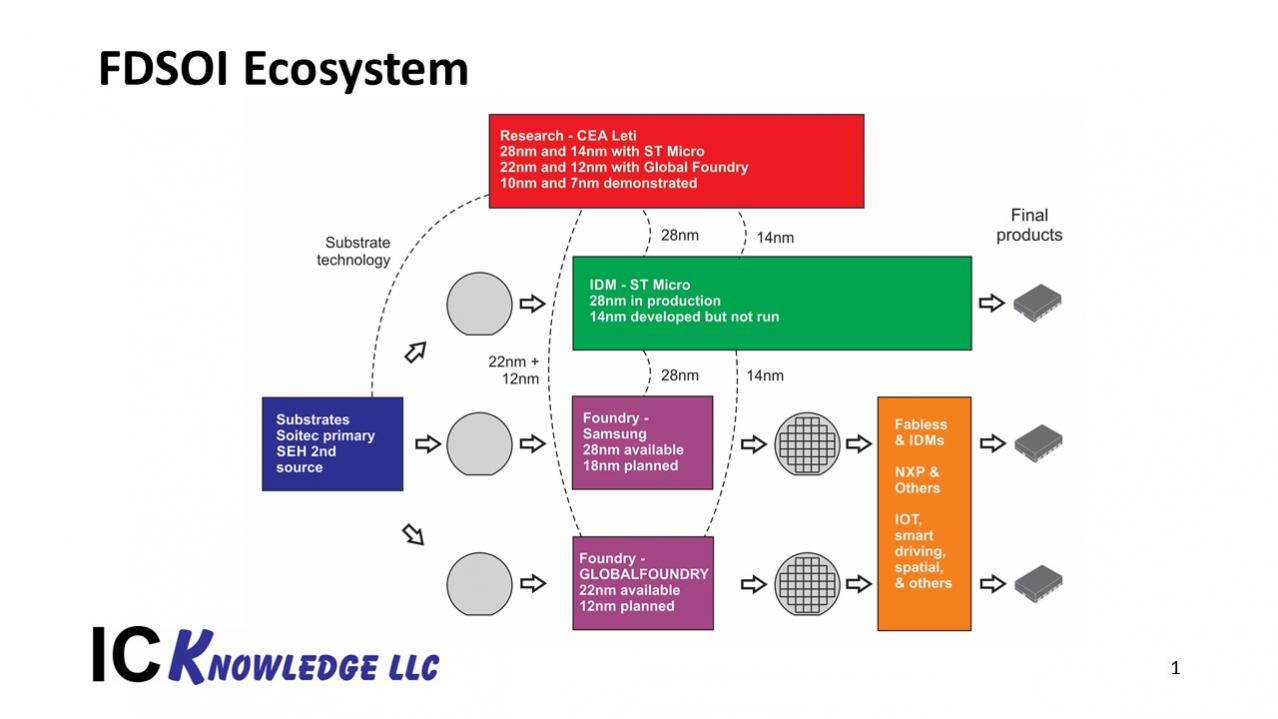

FDSOI Status and Roadmap

FDSOI is gaining traction in the market place. At their foundry forum in May, Samsung announced they have 17 FDSOI products in high volume manufacturing (you can read Tom Dilliger’s write up of the Samsung Foundry Forum here). At SEMICON West in July, GLOBALFOUNDRIES (GF) announced FDSOI design wins worth $2 billion dollars in … Read More

Semicon West – The FDSOI Ecosystem

At Semicon West last week I attended presentations by Soitec and CEA Leti, and had breakfast with CEA Leti CEO Marie Semeria, key members of the Fully Depleted Silicon On Insulator (FDSOI) ecosystem. I have also seen some comments in the SemiWiki forum lately that make me believe there is some confusion on the roles of different companies… Read More

CEO Interview: Marie Semeria of LETI

Laboratoire d’électronique des technologies de l’information (LETI) is a French research center, affiliate to the CEA (Commisariat a l’Energie Atomique). Since LETI creation in 1967, this affiliation has two consequences, the money was flowing from the deep pocket of the atomic industry to sustain advanced … Read More