Without data, there is no computing field to talk about, no technology world to awe at and not much of a semiconductor industry to work in. There is no argument that data is the foundational piece for everything, has been to date and will continue to be. While processing an application’s input data is essential to serve the intended… Read More

Tag: cadence

Intel Foundry Services Forms Alliance to Enable National Security, Government Applications

This will be the year of the semiconductor foundry ecosystem, absolutely. Right in between the Samsung SAFE Forum and the TSMC OIP Open Ecosystem Forum, Intel Foundry Services (IFS) just announced a United States Military, Aerospace, and Government (USMAG) Alliance.

Brilliant move, of course, due to the US Government now being… Read More

The Increasing Gap between Semiconductor Companies and their Customers

Semiconductors sit at the heart of the electronics revolution, and the scaling enabled by Moore’s law has had a transformational impact on electronics as well as society. Traditionally, the relationship between semiconductor companies and their customers has been a function of the volume driven by the customer. In very … Read More

Podcast EP112: How Cadence is Revolutionizing Full-Chip Signoff with Certus

Dan is joined by Brandon Bautz, Sr. Group Director of Product Management, responsible for the Cadence silicon signoff and verification product lines in the Digital & Signoff Group.

Dan and Brandon explore the substantial challenges faced by design teams needing to perform full-chip signoff at an accelerated pace for advanced… Read More

Ansys’ Emergence as a Tier 1 EDA Player— and What That Means for 3D-IC

Over its 40+ year history, electronic design automation (EDA) has seen many companies rise, fall, and merge. In the beginning, in the 1980s, the industry was dominated by what came to be known as the big three — Daisy Systems, Mentor Graphics, and Valid Logic (the infamous “DMV”). The Big 3 has morphed over the years, eventually settling… Read More

Samsung Foundry Forum & SAFE™ Forum 2022

It has been an exciting time in the semiconductor industry and the excitement is far from over. Years 2022 and 2023 will be more challenging in many different ways and live activities have just begun. The cornerstones to the semiconductor industry are the foundries so I look forward to the live foundry events coming up in October,… Read More

Podcast EP105: Cadence STA Strategy and Capabilities, Today and Tomorrow with Brandon Bautz

Dan is joined by Brandon Bautz, senior group director of product management responsible for silicon signoff and verification product lines in the Cadence Digital & Signoff Group. Brandon has more than 20 years of experience in chip design and the EDA industry and has been at Cadence for over 10 years.

Dan explores the current… Read More

Unlock first-time-right complex photonic integrated circuits

The capacity and energy efficiency challenges from the growing appetite for high-speed data along with advanced applications such as LIDAR and quantum computing are driving demand for increasingly large-scale photonic integrated circuits (PIC). With an ever-increasing number of components on a single photonic chip, manual… Read More

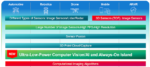

Designing Ultra-Low-Power, Always On IP

It’s popular to use DSP chips for vision processing in diverse applications like ADAS, security cameras and AR. Tensilica has been designing DSP chips and IP since 1997, and their technology was successful enough that Cadence acquired Tensilica back in 2013. At the IP-SoC Silicon Valley 2022 event in April I had the pleasure… Read More

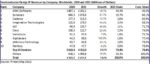

Design IP Sales Grew 19.4% in 2021, confirm 2016-2021 CAGR of 9.8%

Design IP Sales reached $5.45B in 2021, or 19.4% YoY after 16% in 2020, on-sync with semiconductor growth of 26.2% in 2021 according to WSTS. IPnest has released the “Design IP Report” in May 2022, ranking IP vendors by category (CPU, DSP, GPU & ISP, Wired Interface, SRAM Memory Compiler, Flash Memory Compiler, Library and I/O,… Read More