Now that the dust has settled, I will give you my take on the Intel Foundry event. Some might call me a semiconductor event critic as I have attended hundreds of them over the last 40 years starting with the Design Automation Conference in 1984. Foundry events are my favorite because they really are the pulse of the semiconductor industry,… Read More

Tag: cadence

Designing and Simulating Next Generation Data Centers and AI Factories

At NVIDIA’s recent GTC conference, a Cadence-NVIDIA joint session provided insights into how AI-powered innovation is reshaping the future of data center infrastructure. Led by Kourosh Nemati, Senior Data Center Cooling and Infrastructure Engineer from NVIDIA and Sherman Ikemoto, Sales Development Group Director from … Read More

How Cadence is Building the Physical Infrastructure of the AI Era

At the 2025 NVIDIA GTC Conference, CEO Jensen Huang delivered a sweeping keynote that painted the future of computing in bold strokes: a world powered by AI factories, built on accelerated computing, and driven by agentic, embodied AI capable of interacting with the physical world. He introduced the concept of Physical AI—intelligence… Read More

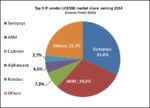

Design IP Market Increased by All-time-high: 20% in 2024!

Design IP revenues achieved $8.5B in 2024 and this is an all-time-high growth of 20%. Wired Interface is still driving Design IP growth with 23.5% but we see the Processor category also growing by 22.4% in 2024. This is consistent with the Top 4 IP companies made of ARM (mostly focused on processor) and a team leading wired interface… Read More

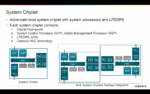

Embracing the Chiplet Journey: The Shift to Chiplet-Based Architectures

The semiconductor industry is facing a paradigm shift. Traditional scaling, once driven by Moore’s Law, is slowing down. For years, moving to smaller process nodes led to lower transistor costs and better performance. However, scaling from node to node now offers fewer benefits as wafer costs rise much more than the historical… Read More

Accelerating Automotive SoC Design with Chiplets

The automotive industry is evolving rapidly with the increasing demand for intelligent, connected, and autonomous vehicles. Central to this transformation are System-on-Chip (SoC) designs, which integrate multiple processing units into a single chip for managing everything from safety systems to in-car entertainment.… Read More

Accelerating Electric Vehicle Development – Through Integrated Design Flow for Power Modules

The development of electric vehicles (EVs) is key to transitioning to sustainable transportation. However, designing high-performance EVs presents significant challenges, particularly in power module design. Power modules, including inverters, bulky DC capacitors, power management ICs (PMICs), and battery packs, … Read More

Compiler Tuning for Simulator Speedup. Innovation in Verification

Modern simulators map logic designs into software to compile for native execution on target hardware. Can this compile step be further optimized? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas.… Read More

Podcast EP262: How AI is Changing Semiconductor Design with Rob Knoth

Dan is joined by Rob Knoth, Solutions Architect in the Strategy and New Ventures group at Cadence. He is a technologist focusing on corporate strategy and the interfaces between domain specific solutions. A key area of expertise is the digital implementation of safety critical and high reliability systems. He has extensive experience… Read More

Podcast EP255: The Growing Proliferation of Semiconductors and AI in Cars with Amol Borkar

Dan is joined by Amol Borkar, Product Marketing Director at Cadence. Since joining in 2018 as a senior product manager, he has led the development of many successful hardware and software products, including Tensilica’s latest Vision 331 and Vision 341 DSPs and 4DR accelerator targeted for various vision, automotive and AI edge… Read More