TowerJazzis a specialty foundry that provides IC manufacturing into several markets, like: RF, high-performance analog, power, imaging, consumer, automotive, medical, industrial and aerospace/defense. In June there was a presentation from Ofer Tamir of TowerJazz at DACin the Cadence theatre, so I had a chance this week … Read More

Tag: cadence

How Sonics Uses Jasper Formal Verification

The Jasper part of Cadence announced jointly with Sonics a relationship whereby Sonics uses JasperGold Apps as part of their verification. I talked to Drew Wingard, the CTO, about how they use it.

One way is during the day when their design engineers use Jasper as part of their verification arsenal. Interestingly it is the design… Read More

Semiconductor Safety

Semiconductors and automotive are now like peanut butter and jelly. Certainly you can have one without the other but why would you? I remember when a car first talked to me telling me that the door was ajar. It sounded more like, “the door is a jar” but I got the point. Now my car tells me just about everything including what is wrong with… Read More

In-Design DFM Signoff for 14nm FinFET Designs

While FinFET yield controversy is going on, I see a lot being done to improve that yield by various means. One prime trend today, it must be, it’s worthwhile, is to pull up various signoffs as early as possible during the design cycle. And DFM signoff is a must with respect to yield of fabrication. This reminds me about my patents filed… Read More

What Presentations to Attend During IP-SoC 2014 ?

Will you go to Grenoble next week to attend to IP-SoC? I will do it and will certainly listen to these Keynote Talks:

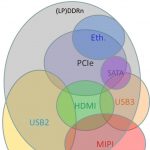

- “Platform IP: the next wave for SOCs from IoT to Datacenter” by Tony King-Smith, Executive Vice President, Marketing , Imagination Technologies

- “From Server-class to IoT SoCs: Enabling System

Cadence Mixed Signal Technology Forum

Yesterday was Cadence’s annual mixed-signal technology forum. I think that there was a definite theme running through many of the presentations, namely that wireless communication of one kind or another is on a sharp rise with more and more devices needing to connect to WiFi, Bluetooth and so on. This was most obvious during… Read More

How ST Designs with Layout Dependent Effects (LDE)

I first visited STat their Agrate, Italy site where Flash memory development is done. At DACthis year Antonio Bogani talked about how ST designs with LDE while using EDA tools and a PDK (Process Design Kit) from Cadence. They recorded the 17 minute presentation, and you can view it herewithout having to register. Antonio’s… Read More

TSMC ♥ Cadence!

One of the questions I routinely ask amongst the fabless semiconductor ecosystem is, “How are the EDA vendors doing?” There are always complaints because, let’s face it, we all like to complain. On occasion however I do hear about a vendor who goes above and beyond the call of duty and it really brightens my day.

Of late,… Read More

Key Collaboration to Enable Designs at Advanced Nodes

In the semiconductor ecosystem, several partners (or better to say stakeholders) join together in the overall value chain to finally output the most coveted chip, err I should say SoC these days. It becomes really interesting when we start analyzing the real value added by each of them, none appears to be less. Well, then to whom … Read More

AMD Design IP Deal with Virage Logic… Oops… Synopsys

Whoever has said that history never repeats itself should read this recent PR from AMD! The news can be summarized in three points:

- Multi-year agreement gives AMD access to a range of Synopsys design IP including interface, memory compiler, logic library and analog IP for advanced FinFET process nodes

- Synopsys acquires rights