I used to joke that my first car could survive a nuclear war. It was a 1971 Volvo sedan (142) that was EMP proof because it had absolutely no semiconductors in the ignition system, just points, condensers and a coil. If you go back to the Model T in 1915 you will see that the “on-board electronics” were not that different. However, today’s… Read More

Tag: cadence

Nine Cost Considerations to Keep IP Relevant –Part2

In the first part of this article I wrote about four types of costs which must be considered when an IP goes through design differentiation, customization, characterization, and selection and evaluation for acquisition. In this part of the article, I will discuss about the other five types of costs which must be considered to enhance… Read More

Nine Cost Considerations to Keep IP Relevant

It’s about 15 years the concept of IP development and its usage took place. In the recent past the semiconductor industry witnessed start of a large number of IP companies across the globe. However, according to Gary Smith’s presentation before the start of 52[SUP]nd[/SUP] DAC, IP business is expected to remain stagnant for next… Read More

A Brief History of FPGA Prototyping

Verifying chip designs has always suffered from a two-pronged problem. The first problem is that actually building silicon is too expensive and too slow to use as a verification tool (when it happens, it is not a good thing and is called a “re-spin”). The second problem is that simulation is, and has always been, too slow.

When Xilinx… Read More

Moving up Verification to Scenario Driven Methodology

Verification complexity and volume has always been on the rise, taking significant amount of time, human, and compute resources. There are multiple techniques such as simulation, emulation, FPGA prototyping, formal verification, post-silicon testing, and so on which gain prominence in different situations and at different… Read More

What’s the Difference between Emulation and Prototyping?

Increasing system complexity requires constant focus on the optimal verification methodology. Verification environments incorporate a mix of: transaction-based stimulus and response monitors, (pseudo-)random testcase generation, and ultimately, system firmware and software. RTL statement and assertion coverage… Read More

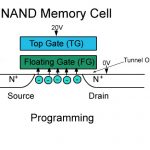

Adding NAND Flash Can Be Tricky

As consumers, we take NAND flash memory for granted. It has worked its way into a vast array of products. These include USB drives, SD cards, wearables, IoT devices, tablets, phones and increasingly SSD’s for computer systems. From the outside the magic of flash memory seems quite simple, but we have to remember that this is a technology… Read More

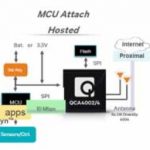

Xtensa core in Qualcomm low-power Wi-Fi

Wi-Fi has this reputation as being a power hog. It takes a relatively big processor to run at full throughput. It is always transmitting all over the place, and it isn’t very efficient at doing it. Most of those preconceived notions arose from older chips targeting the primary use case for Wi-Fi in enterprise and residential environments.… Read More

Older Nodes Get New Life With Ultra Low Power Variants for IoT

Ever since I can remember, and I’ve been in EDA since the early 80’s, new process development has largely focused on the latest nodes. Trailing nodes were quickly put into support mode. New nodes benefited the most from static and dynamic voltage reduction efforts, as well as improvements in flows and performance. Only a small number… Read More

My Tryst with Semiconductors and EDA

Yes, today I realize it feels like a tryst with semiconductors. In actual meaning; it wasn’t a love affair with semiconductors, but I must say the greatest thing it taught me about how it approaches towards perfection. And that became the guiding principle in my life; how can I do something better. Of course nothing is perfect in life… Read More