I had the privilege to attend a five-day PIC (photonic integrated circuit) training hosted by 7-Penniesand Tektronix in San Jose, CA this week. This training was quite comprehensive and covered photonic materials and platforms, design automation, fabrication, packaging and test. It also included invited talks from photonic… Read More

Tag: cadence

System-level Design for IoT and Automotive

Several years ago a former EDA co-worker went to work for MathWorks, so I started paying a lot more attention to this privately held company that is well known for the MATLAB language and analysis environment. Engineers at MathWorks have created a graphical environment called Simulink for both simulation and model-based design… Read More

A Peek Inside the Global Foundries Photonic Death Star!

Last week I wrote about the Photonics Summit and hands-on training hosted by Cadence Design, PhoeniX Software and Lumerical Solutions and in that article I mentioned that Ted Letavic of Global Foundries laid out a powerful argument for why integrated photonics is a technology that is going main stream. This article dives into … Read More

Protium for the win in software development

Cadence Design Systems is a long-standing provider in hardware emulation, but a relative newcomer to FPGA-based prototyping. In an upcoming lunch and learn session on November 11 in San Jose, Cadence teams will be outlining their productivity strategy. What’s different with their approach and why is this worth a lunch?… Read More

Making your AMS Simulators Faster (webinar)

I’ve been following Cadence Design Systems ever since it was formed in 1988 by the merger of SDA Systems and ECAD, Inc. At that time I was working at Silicon Compiler Systems, soon to be acquired by Mentor Graphics. ClioSoft is another company that I’ve known about for several years now, mostly for their design management… Read More

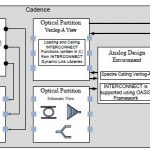

You’re Going to Want to Attend the Cadence Photonics Summit Workshop, October 19-20

Photonics IC’s (PIC’s) are used to transmit and receive data through a (single-mode or multi-mode) optical fiber carrier, and provide the requisite electro-optical conversion for system integration. The architecture of the PIC spans the full characteristics of data transmission and reception:

- light generation

Typically,… Read More

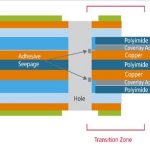

"Rigid-Flex Design is Coming"

Printed circuit boards that incorporate a combination of traditional PCB technology with flexible substrates, aka rigid-flex designs, have enabled an increasing variety of product designs, that leverage the unique physical form factor and lightweight options that rigid-flex technology offers. Yet, this technology requires… Read More

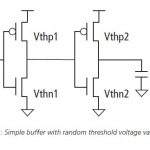

Solutions for Variation Analysis at 16nm and Beyond

Variation is still the tough nut to crack for advanced process nodes. The familiar refrain of lower operating voltages and higher performance requirements make process variation an extremely important design consideration. As far back as the early 2000’s design teams have been looking for a better approach to model variation… Read More

MIPI DevCon 2016: Opened to non-MIPI Members!

The MIPI Alliance was founded in 2003 by large IDM to standardize chip-to-chip interfaces in the wireless phone (mobile) segment. The various MIPI specifications (CSI, DSI, DigRF and many more) have been adopted by the application processor chip makers (usually large IDM or fabless, like Intel or Qualcomm initially and many … Read More

IC and System Design for Mobile and Wearable Devices!

The Linley Mobile and Wearable Conference is coming up so let’s take a look at what is in store for us. Bernard Murphy, Tom Simon, and I will be covering the event live for SemiWiki and we will also be doing a book giveaway/signing for our new “Prototypical” book (compliments of S2C Inc.) during the networking event on Tuesday evening.… Read More