Apache is one of the brightest stars in the EDA universe. Paul McLellan has done a nice job covering them before and after the Ansys acquisition. Check out the Apache SemiWiki landing page HERE. The Apache wikis are also very well done and it has been a pleasure working with the Apache marketing team. Expect more innovative things … Read More

Tag: ansys

Customers Talk About Reliability, Low-Power and 3D

At DAC in San Francisco this year, Apache once again have a mixture of presentations by customers on their use of Apache tools and presentations by Apache themselves on their products. Most of the customer presentations are given just once, but the product presentations are given multiple times over the three days.

I think one of… Read More

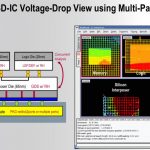

RedHawk: On to the Future

For many, maybe most, big designs, Apache’s RedHawk is the signoff tool for analyzing issues around power: electromigration, power supply droop, noise, transients and so on. But the latest designs have some issues: they are enormous (so you can’t just analyze them naively any more than you can run a Spice simulation… Read More

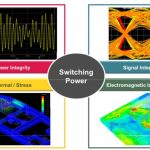

Power Issues for Chip and Board: webinar

Last month Brian Bailey at EDN moderated an interesting webinar about power issues. Unusually, it combined two different domains: doing things by modeling and actually taking measurements off real chips and boards. The two participants were Arvind Shanmugavel from the Apache subsidiary of Ansys, and Randy White from Tektronix.… Read More

Power Issues for Chip and Board

Next week there are two Apache, a subsidiary of Ansys, events. At DesignCon there are a couple of workshops on chip-package-system (CPS). In addition to Apache themselves, each of the two workshops has a number of representatives of leading edge companies doing semiconductor design. I already blogged about this in more detail… Read More

Learning about 3D IC Design and Test, IEEE Workshop on Friday, December 9th in Newport Beach, CA

The IEEE has an Orange Country Chapter of the Components, Packaging and Manufacturing Technology Society who are organizing an all-day workshop, 3D Integrated Circuits: Technologies Enabling the Revolution. This looks to be an informative day with real-world examples in both design and test being presented by over a dozen … Read More

ANSYS Regional Conference

Next Tuesday, August 23rd, is the ANSYS Regional Conference for Silicon Valley. It takes place at the Techmart Network Meeting Center. Apache has three presentations during the day:

- 9.25-9.45 Andrew Yang Introducing Apache Design Solutions

- 11.00-11.30 Methodology for delivering power-efficient designs from concept to

ANSYS/Apache

Last week I met with Andrew Yang, erstwhile CEO of Apache Design Systems and now formally President of Apache Design Inc, a wholly owned subsidiary of ANSYS. The merger formally closed at the start of the month. Within ANSYS Apache is positioned as Chip-aware System-level Engineering Simulation. ANSYS is pretty much completely… Read More

Apache Design Automation acquired by Ansys

We all knew that Apache had filed for an IPO earlier and were just waiting for the timing and price to be revealed. Rumors have been circulating about an acquisition and today we know that the rumors were true asAnsys paid $310 million in cash for Apache.

Ansys stock has surged some 35% over the past twelve months:

Products

This acquisition… Read More