You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Key Takeaways:

- Expanded Multi-Die Solution: Arteris showcases its foundational technology for rapid chiplet-based innovation. Check out the multi-die highlights video.

- Ecosystem compatibility: Supported through integration with products from major EDA and foundry partners, including Cadence, Synopsys, and global

…

Read More

Formal verification methods are being adopted at a fast pace as a complement to traditional verification methods like functional simulation for IP blocks in SoC designs. I had a video meeting with Max Birtel, co-founder of LUBIS EDA and learned more about their history, products and vision. This company started recently in 2020… Read More

We are excited to announce that Truechip, a leading provider of Verification IP solutions, will be actively participating at DAC 2024, taking place from June 23-25 at Moscone West, San Francisco, CA. This event is a pivotal gathering for professionals in the verification industry, and Truechip’s presence will be a highlight … Read More

I am pleased to introduce Truechip to the SemiWiki community. Truechip is a leader in the IP Verification – Design and Verification solutions market, one of the fastest growing market segments we track. Truechip has been serving customers for more than 10 years specialization in VIP integration, customization and SOC Verification.… Read More

Bernard Murphy and I spent time with the SmartDV folks in preparation for the Design Automation Conference later this month. Bernard is an internationally recognized verification expert so his feedback is often sought after by emerging and leading verification companies, absolutely. Verification IP is a crowded market so … Read More

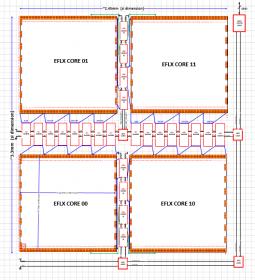

"The Year of the eFPGA" 2017 Recapby Tom Dillinger on 12-22-2017 at 7:00 amCategories: eFPGA, Flex Logix, FPGA, IP

This past January, I had postulated that 2017 would be the “Year of the Embedded FPGA”, as a compelling IP offering for many SoC designs (link). As the year draws to a close, I thought it would be interesting to see how that prediction turned out.

The criteria that would be appropriate metrics include: increasing capital investment;… Read More

A key application for embedded FPGA (eFPGA) technology is to provide functionality for specific algorithms — as the throughput of this implementation exceeds the equivalent code executing on a processor core, these SoC blocks are often referred to as accelerators. The programmability of eFPGA technology offers additional… Read More

A couple of weeks back I wrote an article about the use of machine learning and deep neural networks in self-driving cars. Now I find that machine learning is also being applied to help build advanced end-to-end QoS (quality of service) solutions for the automotive IC market. With the advent of self-driving cars comes requirements… Read More

Merchant microcontrollers are usually made available in a wide range of variants based on one architecture with different peripheral payloads and packaging options. A couple of companies, notably Cypress with their PSoC families and Silicon Labs with the EFM8 Laser Bee… Read More

Designing SOC’s for markets like automotive and mobile electronics requires taking advantage of every opportunity for optimization. One way to do this is through building a cache coherent system to boost speed and reduce power. Recently, NXP decided to go about this on their automotive MCU based SOC’s by using Arteris’ just-announced… Read More