A product launch nowadays demands shorter runway. SoC designers challenges are not so much in facing the unavailability of proven design capture methodologies or IP’s that could satisfy their product requirements, but more so in orchestrating the integration of all those components to deliver the targeted functionalities… Read More

Tag: alex tan

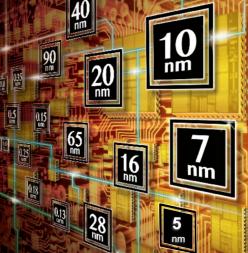

Achieving a Predictable SignOff in 7nm

Designing with advanced-nodes FinFETs such as 7nm node involves a more complex process than prior nodes. As secondary physical effects are no longer negligible, the traditional margin-based approach applied at various design abstraction levels is considered ineffective. Coupled with the increase of device counts, failing… Read More

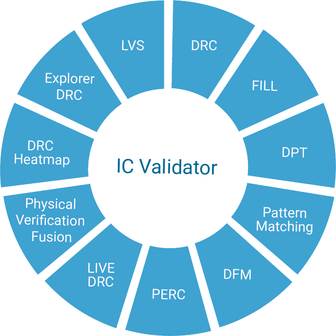

Complex Validation Requires Scalable Measures

The famous Olympic motto Citius, Altius, Fortius, which is the Latin words for “Faster, Higher, Stronger” to a considerable degree can be adapted to our electronics industry. Traditionally the fundamental metrics we used for measuring the quality of results (QoRs) are performance, power, and area (PPA). Amidst… Read More

A Collaborative Driven Solution

Last week TSMC announced the availability of its complete 5nm design infrastructure that enables SoC designers to implement advanced mobile and high-performance computing applications for the emerging 5G and AI driven markets. This fifth generation 3D FinFET design infrastructure includes technology files, PDKs (Process… Read More

Spring Forward with AI

The euphoria of NCAA March Madness seems to spill over into the tech world. The epicenter of many tech talks this month spanning from GPU conference, OCP, SNUG to CASPA has evolved around an increased AI endorsement by many companies and its integration into many silicon driven applications. At this year CASPA Spring Symposium,… Read More

A Preview of Spring Symposium on AIoT

The trend of AI augmentation into many facets of silicon based hardware applications is on the rise. During the CASPA press conference in Santa Clara last week, Silvaco CEO David Dutton and SiFive VP, GM Christopher Moezzi were present to share their insights.

Silvaco CEO David Dutton mentioned that we are in new era in which many… Read More

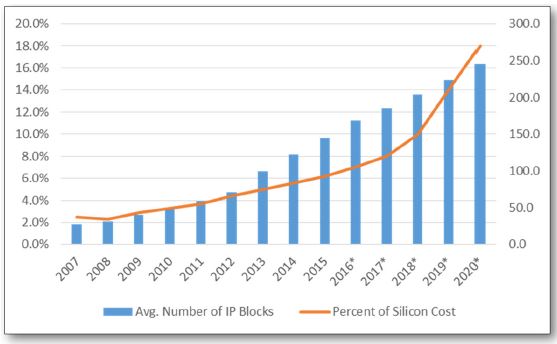

Accelerating Post-Silicon Debug and Test

The recent growing complexity in SoC designs attributed to the increased use of embedded IP’s for more design functionalities, has imposed a pressing challenge to the post-silicon bring-up process and impacting the overall product time-to-market.

According to data from Semico Research, more than 60% of design starts contain… Read More

Data Management Challenges in Physical Design

IC physical design (PD) teams face several challenges while dealing with tapeout schedules. With shrinking process nodes and stringent PPA targets, the complexity of physical design flows and EDA design tools has increased multifold. In addition the amount of design data that needs to be managed has also increased exponentially.… Read More

Switch Design Signoff with IC Validator

The surge of network traffic at the data centers has driven to an increase in network bandwidth, doubling every 12-15 months according to a study conducted on Google’s data centers. The primary drivers to this uptick include the proliferation of cloud computing, more distributed storage architecture, emerging applications… Read More

Specialized AI Processor IP Design with HLS

Intelligence as in the term artificial intelligence (AI) involves learning or training, depending on which perspective it is viewed from –and it has many nuances. As the basis of most deep learning methods, neural network based learning algorithms have gained usage traction, when it was shown that training with deep neural network… Read More