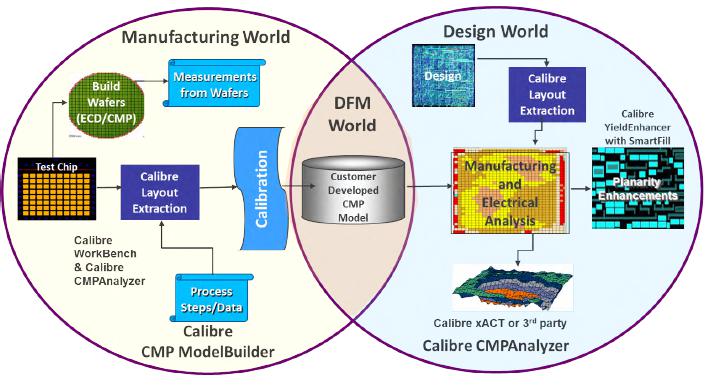

CMP (Chemical Mechanical Planarization or also known as Chemical Mechanical Polishing) is a wafer fabrication step applied generally after a chemical deposition –intended to smoothen and to flatten (planarize) wafer surfaces with the combination of chemical and mechanical forces. Developed at IBM and since its introduction… Read More

Tag: alex tan

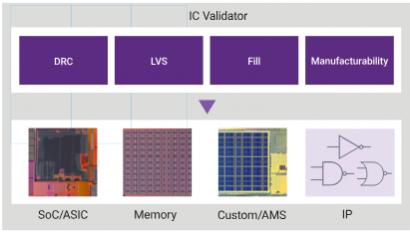

Physical Verification with IC Validator

If a picture worths a thousand words, a tapeout quality SoC design with billions of polygons would compose a good book. To proofread this final design transformation format requires a foundry driven DRC/LVS signoff solution that nowadays is becoming more complex with further process scaling and shrinking pitch dimension.

Despite… Read More

Photonics with CurvyCore

As a preferred carrier to data or energy, photonics technology is becoming broad and diverse. In IC design, silicon-photonics technology has been the enabler of new capabilities and has revolutionized many applications as Moore’s-based scaling started to experience a slowdown. It acts as new on-chip inductor in HPC design … Read More

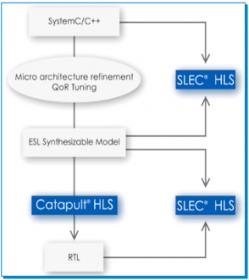

Sequential Equivalency Checks in HLS

Higher level synthesis (HLS) of an IP block involves taking its high-level design specification –usually captured in SystemC or C++, synthesizes and generates its RTL equivalent. HLS provides a faster convergence path to design code stability, promotes design reuse and lowers front-end design inception cost.

HLS and Mentor… Read More

Design Compiler – Next Generation

Back in 1986, Synopsys started out with a synthesis product by name of SOCRATES, which stands for Synthesis andOptimization ofCombinatorial logic usingRule-basedAndTechnology independentExpertSystem. It is fair to say that not many designers know that was the birth name of what eventually turns out to be a very successful… Read More

Webinar: Tanner and ClioSoft Integration

A fusion of digital and analog IC circuits, mixed signal ICs are key components to many applications including IoTs, automotive, communications and consumer electronics –acting as enabler to bidirectional conversion of signals between analog domain derived from various audio, temperature and visual sensors to digital… Read More

Fusion Synthesis for Advanced Process Nodes

Synopsys recently unleashed Fusion Compiler™, a new RTL-to-GDSII product that enables a data-driven design implementation by revamping Design Compiler architecture and leveraging the successful Fusion Technology –seamlessly fusing the logical and physical realms to produce predictable QoR. It is a long-awaited… Read More

The Changing Face of IP Management

Aristotle once said “The whole is greater than the sum of its parts”. The notion of synergism echoes the importance of leveraging design IPs to the maximum extent with the rest of the system under development, in order to ensure a successful SoC design outcome in a shorter development cycle.

SoC design cost and entry point

For over… Read More

Parasitic Extraction for Advanced Node and 3D-IC Designs

Technology scaling has made positive impacts on device performance, while creating challenges on the interconnects and the fidelity of its manufactured shapes. The process dimension scaling has significantly increased metal and via resistance for advanced nodes 7nm and onward, as shown in figures 1a,1b. Similar to a fancy… Read More

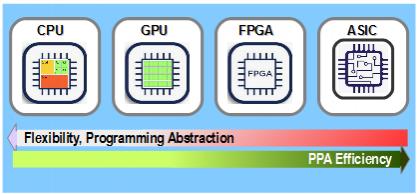

Webinar: ASIC and FPGA Functional Verification Study

ASIC or FPGA? Each design style has earned designers’ votes depending on the level of urgency, application complexity and funding of their assigned projects. While it is feasible to transition from ASIC to FPGA design or vice versa, such a move is usually done across project refresh instead of midcourse.