Cadence has clearly found its groove with Intelligent System Design, something that Lip-Bu reinforced in the CadenceLIVE kickoff keynote on Tuesday, August 11th. Anirudh Devgan, president of Cadence, continued to discuss the theme in his keynote on Wednesday, August 12th with his equally consistent subtitle—”Strength… Read More

Tag: 3dic

A Quick TSMC 2019 Tech Symposium Overview

This year TSMC did a FinFET victory lap with the success of 16nm, 12nm, 10nm, and 7nm. It really is well deserved. Even though TSMC credits the ecosystem and customers, I credit TSMC and their relationship with Apple since it has pushed us all much harder than ever before. TSMC CEO C.C. Wei summed it up nicely in his keynote: Innovation,… Read More

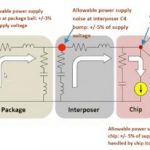

Power Integrity from 3DIC to Board

The semiconductor industry has built decades of success on hyper-integration to increase functionality and performance while also reducing system cost. But the standard way to do this, to jam more and more functionality onto a single die, breaks down when some of the functions you want to integrate are built in different processes.… Read More

The Death of Moore’s Law

For the last several years, people have predicted the end of Moore’s Law. The reasoning is that there is a limit at which one can’t shrink transistors any further. A reoccurring comment has been “You can’t divide an atom.” I had assumed that its demise would be at the hands of a new paradigm like quantum computing. Now, with Intel’s … Read More

TSMC 10nm Readiness and 3DIC

At the TSMC Technology Symposium last month Suk Lee presented a lot of information on design enablement. Suk is an interesting guy with a unique background in ASIC, Semiconductor, EDA, and now Foundry. In baseball terms that would be like playing infield, outfield, home plate, and umpire!

Around the turn of the millennium Suk actually… Read More

TSV Modeling Key for Next Generation SOC Module Performance

The use of silicon interposers is growing. Several years ago Xilinx broke new ground by employing interposers in their Virtex®-7 H580T FPGA. Last August Samsung announced what they say is the first DDR4 module to use 3D TSV’s for enterprise servers. Their 64GB double data rate-4 modules will be used for high end computing where … Read More

EDPS: Fins and FinFETs

Look at those dolphins with fins on their backs. Did you know that FinFETs are actually named after them since Chenming Hu and his team though that they looked like a fish’s fin? And since they invented FinFETs they got to name them too. But those dolphins also mean that it is nearly time for this years Electronic Design Process… Read More

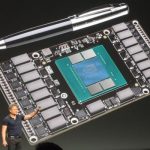

Will 3DIC Ever Be Cheap Enough for High Volume Products?

More news from the 3DASIP conference. Chet Palesko of SavanSys Solution had an interesting presentation with the same title as this blog (although this blog draws from several other presentations too). Chet took a look at what aspects of 3D are likely to get cheaper going forward. He took as a starting point that stuff that is not … Read More

3D, The State of the State

I have been at the 3D ASIP conference that is held every year in Burlingame. It is far and away the best place to get a snapshot on what is going on in 3D (and 2.5D) IC design each year. One of the presentations was by the guys from Yole on where the industry is right now. Other presentations were on pathfinding, power reduction (did you know… Read More

3DIC in Burlingame

Every year in December is what I think of as the main 3D IC conference where you can get up to speed on all the latest. Officially it is called 3D Architectures for Semiconductor and Packaging or 3D ASIP. It is held in the Hyatt Regency in Burlingame (the one right by 101 near the airport). This year it is from December 10-12th.

The first… Read More