You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Late in January it is DesignCon at the Santa Clara convention center from January 28th-31st. Details are here.

On Tuesday from 11.05 to 11.45 Apache and Ansys will be presenting on Thermal Co-analysis of 3D IC/packages/system. This is being presented by a whole team of people: Stephen Pan, senior product specialist at ANSYS; Norman… Read More

There is obviously a lot going on in 3D IC these days. And I don’t mean at the micro level of FinFETs which is also a way of going vertical. I mean through-silicon-via (TSV) based approaches for either stacking die or putting them on an interposer. Increasingly the question is no longer if this technology will be viable (there… Read More

Once upon a time (since every good story begins that way), I worked on 10kg, 70 mm diameter things that leapt out of tubes and chased after airplanes and helicopters. The electronics for these things were fairly marvelous, in the days when surface mount technology was in its infancy and having reliability problems in some situations.… Read More

At advanced process nodes, variation and its effects on the design become a huge challenge. Join Cadence® Virtuoso® experts for a series of technical webinars on variation-aware design. Learn how to use advanced technologies and tools to analyze and understand the affects of variation. We’ll introduce you to the latest Virtuoso… Read More

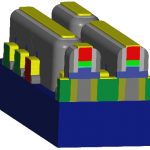

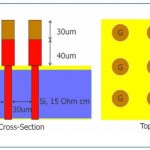

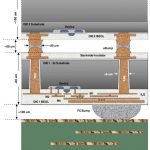

The press has been buzzing about 3D everything for the past few years, so when it comes to IC design it’s a fair question to ask how would you actually extract 3D IC structures for use by analysis tools like a circuit simulator. I read a white paper by Christen Decoin and Vassilis Kourkoulos of Mentor Graphics this week and became… Read More

As 2D device scaling becomes impractical, 3D-IC integration is emerging as the natural evolution of semiconductor technology; it is the convergence of performance, power and functionality. Some of the benefits of 3D-IC, such as increasing complexity, improved performance, reducing power consumption and decreasing footprints,… Read More

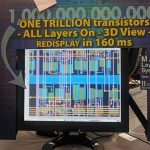

There are only a handful of billion transistor IC designs in existence today, so when an EDA company touts 1 trillion transistor IC layout editing then I take notice. This year at DAC I met with Katherine Hayes and Karen Mangum of Micro Magic to get an update on their IC layout tools.… Read More

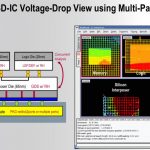

For many, maybe most, big designs, Apache’s RedHawk is the signoff tool for analyzing issues around power: electromigration, power supply droop, noise, transients and so on. But the latest designs have some issues: they are enormous (so you can’t just analyze them naively any more than you can run a Spice simulation… Read More

At the GSA silicon summit yesterday the first keynote was by Subramanian Iyer of IBM on Keeping Moore’s Law Alive. He started off by asking the question “Is Moore’s Law in trouble?” and answered with an equivocal “maybe.”

Like some of the other speakers during the day, he pointed out that … Read More

EDPS: 3D ICs, part IIby Paul McLellan on 04-12-2012 at 10:00 pmCategories: EDA, Events

Part I is here.

In the panel session at EDPS on 3D IC a number of major issues got highlighted (highlit?).

The first is the problem of known-good-die (KDG) which is what killed off the promising multi-chip-module approach, perhaps the earliest type of interposer. The KDG problem is that with a single die in a package it doesn’t… Read More