I spent some quality time with Subi Kengeri, Vice President, Technology Architecture, Office of the CTO, GLOBALFOUNDRIES in Las Vegas during CES. Great guy, he worked at Silicon Access, Virage and TSMC before GF. One thing you should know about embedded memory guys, SRAM is the first thing that goes through a new process so they … Read More

Tag: 14nm

Intel’s New Tablet Strategy Brings Ivy Bridge to the Forefront

In an article published this week in microprocessor report and highlighted in Barron’s, Linley Gwennap makes the argument that Intel should stay the course and fix the PC instead of trying to offset its declines with sales into the Smartphone and Tablet space. He cites that lower PC sales growth was due to a dramatic slowdown in processor… Read More

FinFET Modeling and Extraction at 16-nm

In 2012 FinFET is one of the most talked about MOS technologies of the year because traditional planar CMOS has slowed down on scaling below the 28nm node. To learn more about FinFET process modeling I attended a Synopsys webinar where Bari Biswas presented for about 42 minutes include a Q&A portion at the end.

Bari Biswas, Synopsys… Read More

How Apple Plans to Leverage Intel’s Foundry

Tim Cook’s strategy to disengage from Samsung as a supplier of LCDs, memory and processors while simultaneously creating a worldwide supply chain from the remnants of former leaders like Sharp, Elpida, Toshiba and soon Intel is remarkable in its scope and breadth. By 2014, Apple should have in place a supply chain for 500M iOS devices… Read More

IBM Tapes Out 14nm ARM Processor on Cadence Flow

An announcement at the ARM conference was of a joint project to tape out an ARM Cortex-M0 in IBM’s 14nm FinFET process. In fact they taped out 3 different versions of the chip using different routing architectures to see the impact on yield.

This was the first 14nm ARM tapeout, it seems. I’m sure Intel has built plenty … Read More

GlobalFoundries Announces 14nm Process

Today GlobalFoundries announced a 14nm process that will be available for volume production in 2014. They are explicitly trying to match Intel’s timeline for the introduction of 14nm. The process is called 14XM for eXtreme Mobility since it is especially focused on mobile. The process will be introduced just one year after… Read More

How the Apple-Samsung Duel Will Lead to Wintel 2.0

The High Tech Trial of this Century: Apple vs. Samsung may end up being the catalyzing event that advances the established PC Monopolists known as Wintel (Microsoft and Intel) into leadership positions in the new era known as the Mobile Tsunami. Not a chance you say? Consider that the Apple, Samsung War is one that will not be settled… Read More

The Scariest Graph I’ve Seen Recently

Everyone knows Moore’s Law: the number of transistors on a chip doubles every couple of years. We can take the process roadmap for Intel, TSMC or GF and pretty much see what the densities we will get will be when 20/22nm, 14nm and 10nm arrive. Yes the numbers are on track.

But I have always pointed out that this is not what drives… Read More

Smart mobile SoCs: Intel

Talk about an unusual position. Intel finds themselves very much currently outside when it comes to mobile SoCs for phones and tablets. After several attempts at soul-searching and a true understanding of the term “low-power” (not meaning 3W, but instead < 1W), they finally have a part – in the form of “Medfield”, aka the Atom… Read More

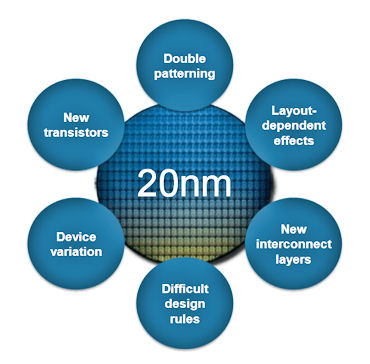

Sagantec Update: More EDA Consolidation!

Adding sophisticated 2D dynamic compaction technology to address 20nm and 14nm challenges. Santa Clara, California – May 3 ,2012 – Sagantec today announced that it has acquired Dutch startup NP-Komplete Technologies BV (Eindhoven, The Netherlands) for its physical design compaction and migration solutions based on a sophisticated… Read More