Being that TSMC and Solido are founding members of SemiWiki, you should be able find out everything you ever wanted to know on their respective landing pages. If not, just ask a question in the SemiWiki forum and I can assure you it will be answered in great detail. And here are some other interesting 2015 factoids from Solido:… Read More

Tag: 10nm

Are Standard Cell Libs, Memories and Mixed-signal IP Availabe at 7nm FF?

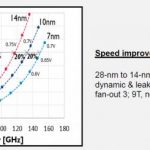

More than 500 designers (562) have responded to a survey made in 2015 by Synopsys. Answering to the question “What is the fastest clock speed of your design?” 56% have mentioned a clock higher than 500 MHz (and still 40% higher than 1 GHz). If you compare with the results obtained 10 years ago, the largest proportion of answers was for… Read More

EUV is coming but will we need it?

I have written multiple articles about this year’s SPIE Advanced Lithography Conference describing all of the progress EUV has made in the last year. Source power is improving, photoresists are getting faster, prototype pellicles are in testing, multiple sites around the world are exposing wafers by the thousands and more. … Read More

10nm SRAM Projections – Who will lead

At ISSCC this year Samsung published a paper entitled “A 10nm FinFET 128Mb SRAM with Assist Adjustment System for Power, Performance, and Area Optimization. In the paper Samsung disclosed a high density 6T SRAM cell size of 0.040µm[SUP]2[/SUP]. I thought it would be interesting to take a look at how this cell size stacks … Read More

Intel EUV Photoresist Progress and ASML High NA EUV

SPIE Days 3 and 4:

Anna Lio of Intel presented EUV resists: What’s next?

Intel wants to insert EUV at 7nm but it has to be ready and economical. Critical Dimension Uniformity (CDU), Line Width Roughness (LWR) and edge placement/stochastics are all stable on 22nm, 14nm and 10nm pilot lines.… Read More

ASML and IMEC EUV Progress

Day 1 of the SPIE conference featured a number of customer updates on the status of their EUV programs. On Tuesday morning we got to hear ASML’s update on their work.… Read More

TSMC and Intel on the Long Road to EUV

Today is the first day of the SPIE Advanced Lithography Conference and Extreme Ultraviolet (EUV) updates were a big focus.… Read More

Coventor ASML IMEC: The last half nanometer

On Tuesday evening December 8[SUP]th[/SUP] at IEDM, Coventor held a panel discussion entitled the “The last half nanometer”. Coventor is a leading provider of simulation software used to design processes. This is my third year attending the Coventor panel discussion at IEDM and they are always excellent with very strong panels… Read More

Calibre in the Middle of Semiconductor Ecosystem

Albert Einsteinhad said, “In the middle of difficulty lies opportunity”. In today’s world dominated by technology, or I must say internet which has initiated collaborative information sharing, “leading from the middle” is the new mantra of life.… Read More

Intel Analyst Day – More Capex-Less Losses- PCs Slow/Stabilizing- More M&A?

Like other semi stocks we could see a relief rally as the analyst day is likely to be better than previous news flow- Not much new to tell. Most all of the bad news has been wrung out of the stock- 10nm delays, slowing PCs, tablet losses- the bar has been reset on most issues to “beatable levels”.… Read More