Just a reminder, the semiconductor industry is doing quite well thanks to the fabless semiconductor ecosystem. TSMC, my economic bellwether, reported another great month with a 32% increase over August 2011 and a 16% increase over January-August 2011. TSMC is forecasting Q3 at a 7% increase over Q2, which was an amazing 21% increase over Q1. Congratulations to everyone in the ecosystem on the amazing TSMC 28nm ramp!

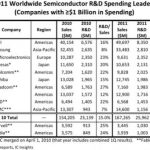

The other great news is that according toIC Insights, semiconductor R&D spending will hit a record high of $53.4B in 2012. Great news and it came out on September 4[SUP]th[/SUP] which is my birthday. R&D is now 16.2% of the total $329.9B semiconductor industry sales and I am now well into my 50’s. Seriously, I make 52 look good.

It is interesting to see that 7 of the top 12 semiconductor R&D spenders are fabless and all 7 are TSMC customers. In fact every company on this list are TSMC customers including Intel and Samsung. I think another interesting number would be total fabless R&D dollars spent per year which would include all companies that are part of the fabless semiconductor ecosystem. Even if you just took ARM, ARM customers, and the foundries that make the ARM based products it would be greater than ONE TRILLION DOLLARS as compared to Intel’s $8.3B R&D spend in 2011. That is what you call crowd sourcing and the crowd will win every time. In case you had not guessed, I’m short on Intel and that was even before Intel’s revenue warning last week.

In July 2012, TSMC chief executive Morris Chang noted that his company’s 2012 R&D budget is now double the amount spent in 2009 (which was $656 million), in addition to raising capital expenditures 13% to an all-time high of $8.25 billion compared to $7.33 billion in 2011. TSMC’s R&D–to-sales ratio stood slightly above 8% in 1H12 versus 7.9% in 2011, 5.1% in 2005 and 3.1% in 2000.

It is also interesting to see that US based companies spent 57% of the total semiconductor R&D money while Japan spent 17%, EU 10%, Taiwan 8%, South Korea 7%, and China 1%. TSMC hit the top 10 R&D spenders in 2010 and is spending almost twice as much as the 12% published average. Also note that TSMC’s R&D increased 1% while Intel’s decreased 1%.

Capital expenditures (CAPEX), not to be confused with R&D spending, are also on the rise. The chart says $6B for TSMC but that is wrong. In fact, TSMC’s CAPEX in 2012 is currently $8B and could hit $8.5B by year end. TSMC is expected to increase its CAPEX by 25%, from $8B in 2012 to $10B during 2013 for 28nm expansion, 20nm ramp, and 16nm (FinFET) development. Intel is at $12.5B and Samsung is at $12.2B. Both Intel and Samsung’s 2013 CAPEX should exceed $13B but will certainly not grow 25%.

With the continuing migration from IDM (fab) to fab light to fabless expect to see TSMC outperform the semiconductor industry for years to come. Also expect to see me outperform the 50’s well into my 60’s.