You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 158

[name] => Foundries

[slug] => semiconductor-manufacturers

[term_group] => 0

[term_taxonomy_id] => 158

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 1379

[filter] => raw

[cat_ID] => 158

[category_count] => 1379

[category_description] =>

[cat_name] => Foundries

[category_nicename] => semiconductor-manufacturers

[category_parent] => 0

[is_post] =>

)

The foundry executive shuffle continues at Samsung, GlobalFoundries, and TSMC. Some expected, some not, the needs of the many outweigh the needs of the few. As I have mentioned before I have no inside knowledge as to who will be named as Dr. Morris Chang’s successor but here is my candidate for the next TSMC CEO.

First, the executive… Read More

The war of words continues, when will it end? I consider myself a reasonably educated and informed person, certainly above average by U.S. standards, yet I have no idea why the U.S. Government continues to write checks they cannot cash and I don’t know who to believe in the resulting media blasts. I truly miss the days of Ross… Read More

The 5[SUP]th[/SUP] annual TSMC OIP Forum was last week and thankfully there were no surprises with the exception of how many people asked me who I think will be the next TSMC CEO. Certainly I have no idea but I would be happy to use my incredible powers of deductive reasoning to determine who it will be.

The TSMC Open Innovation Platform®… Read More

One of TSMC’s two big Silicon Valley events each year is the Open Innovation Platform (OIP) Forum. This year it is on Tuesday October 1st. It is in the San Jose Convention Center and starts at 9am (registration opens at 8am). Pre-registration to attend is now open here or click on the image to the right.

From 9.10 to 9.40 is the … Read More

Today Micron announced that it is shipping 2GB Hybrid Memory Cube (HMC) samples. The HMC is actually 5 stacked die connected with through-silicon-vias (TSVs). The bottom die is a logic chip and is actually manufactured for Micron in an IBM 32nm process (and doesn’t have any TSVs). The other 4 die are 4Gb DRAM die manufactured… Read More

The legend of Intel being two process nodes ahead of the rest of the industry is quickly coming to an end. To come to terms with this you need to do an apple to apple comparison which is what I will do right here, right now.

First and foremost let’s compare SoC silicon delivery since SoCs are driving the semiconductor industry and will … Read More

This time it is between the suppliers of semiconductor manufacturing equipments. And they are among the top ranked global peers. Applied Materials Inc., holding the numero uno position in sales of chip manufacturing equipments in 2012, agreed to acquire Tokyo Electron Ltd, the third in that ranking. Gary Dickerson of Applied… Read More

The existence of TSMC’s Open Innovation Platform (OIP) program further sped up disaggregation of the semiconductor supply chain. Partly, this was enabled by the existence of a healthy EDA industry and an increasingly healthy IP industry. As chip designs had grown more complex and entered the system-on-chip (SoC) era, the amount… Read More

There was some serious backlash to the “Intel Bay Trail Fail” blog I posted last week, mostly personal attacks by the spoon fed Intel faithful, but there are however some very interesting points made amongst the 30+ comments so be sure and read them when you have a chance.

The Business insider article “The iPhone… Read More

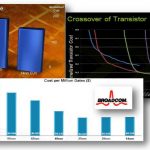

It is beginning to look as if 28nm transistors, which are the cheapest per million gates compared to any earlier process such as 45nm, may also be the cheapest per million gates compared to any later process such as 20nm.

What we know so far: FinFET seems to be difficult technology because of the 3D structure and so the novel manufacturing… Read More

Solving the EDA tool fragmentation crisis