Marc Engel has served as the CEO of Agileo Automation for the past 15 years. Agileo specializes in software solutions for controlling semiconductor production equipment and connecting tools to MES systems using SECS/GEM and OPC-UA standards. Marc started his extensive 25-year engineering career in software development on… Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More

Two Paths for AI in Semiconductor Manufacturing: Platform Integration vs. Point Solutions Semiconductor manufacturing has become one of the…Read More Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

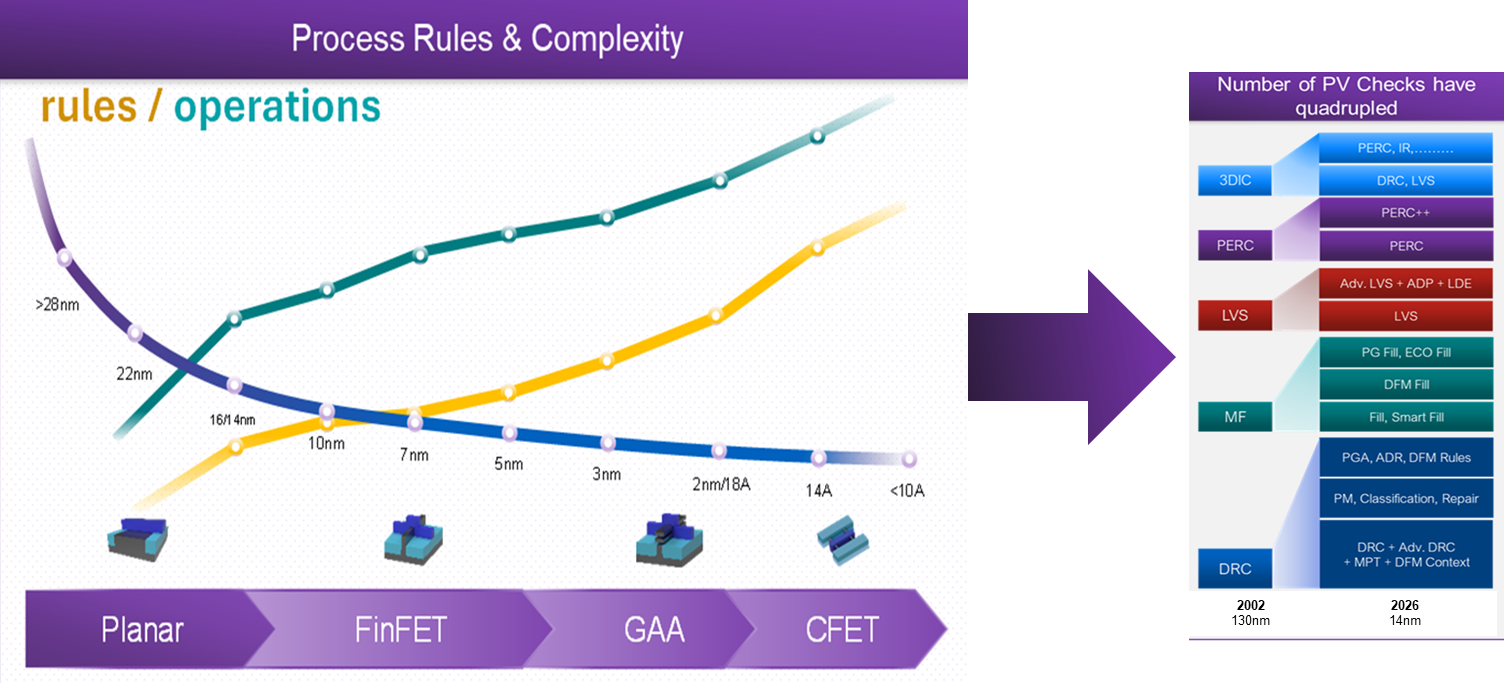

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More

How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read MoreCEO Interview with Dr. Dennis Michaelis of GEMESYS

Dr. Dennis Michaelis is the founder and CEO of the AI chip start-up. With a Ph.D. in Bio-Inspired Computing at the Purdue University in Indiana and a background in electrical engineering, he brings a unique blend of technical expertise and social commitment to the company. His previous role as Regional Director for Anonymous for… Read More

What would you do if you were the CEO of Intel?

One of the most enduring threads in the SemiWiki forum is What would you do if you are the Intel CEO? There are currently 128 responses and more than 45,000 views. It was originally posted March 13th, 2015, after Brain Krzanich was given the CEO position. A different time for sure but an interesting read and the responses keep on coming.… Read More

Stochastic Pupil Fill in EUV Lithography

Pupil fill tradeoff again

EUV lithography continues to be plagued by its stochastic nature.

This stochastic nature is most clearly portrayed by the random fluctuation of the absorbed photon number at a given location. For example, consider an absorbed dose of 10 mJ/cm2 amounts to 6.8 photons of energy 92 eV absorbed in a square … Read More

Consumer memory slowing more than AI gaining

- Consumer memory slowing more than AI gaining causing weakness

- HBM sold out for 2025- HBM is most of Capex- NAND near zero

- Big miss on Q1 guide crushes stock on disappointment

- Positive for Nvidia- Negative for Broadcom/Qualcomm

Micron – AI is wonderful & growing out of bounds while consumer sucks

Micron reported in line… Read More

Intel Presents the Final Frontier of Transistor Architecture at IEDM

IEDM was buzzing with many presentations about the newest gate-all-around transistor. Both Intel and TSMC announced processes based on nanosheet technology. This significant process innovation allows the fabrication of silicon RibbonFET CMOS devices, which promise to open a new era of transistor scaling, keeping Moore’s… Read More

Podcast EP267: The Broad Impact Weebit Nano’s ReRAM is having with Coby Hanoch

Dan is joined by Coby Hanoch, Coby joined Weebit Nano as CEO in 2017. He has 15 years of experience in engineering and engineering management roles, and 28 years of experience in sales management and executive roles.

Coby describes the impact Weebit Nano’s ReRAM technology is having for: Embedded non-volatile memory, in… Read More

If you believe in Hobbits you can believe in Rapidus

– Semicon Japan super crowded but outlook still uncertain/muted

– Slow analysts finally capitulate on weakening 2025 WFE outlook

– Article confirms our view on chip equip lobbying for China sales

– TSMC continues dominate, China slows, Samsung/Intel weak

Semicon Japan crowded but muted

We attended… Read More

TSMC Unveils the World’s Most Advanced Logic Technology at IEDM

There was a lot of discussion at IEDM about the coming shift to gate-all-around (GAA) transistor structures. This new device brings many benefits to continue device scaling, both at the monolithic device level as well as for multi-die design. The path to GAA is not simple, there are new material, process and design considerations… Read More

Ultra Ethernet and UALink IP solutions scale AI clusters

AI infrastructure requirements are booming. Larger AI models carry hefty training loads and inference latency requirements, driving an urgent need to scale AI acceleration clusters in data centers. Advanced GPUs and NPUs offer solutions for the computational load. However, insufficient bandwidth or latency between servers… Read More

Is Intel About to Take Flight?