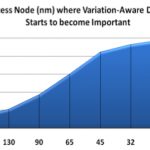

I like to say that “you can’t ignore the physics any more” to point out that we have to worry about lots of physical effects that we never needed to consider. But “you can’t ignore the statistics any more” would be another good slogan. In the design world we like to pretend that the world is pass/fail. But manufacturing is actually a statistical… Read More

From Space-Central to Space-Time Balanced - A Perspective for Moore’s Law 2.0 and A Holistic Paradigm for EmergenceA friend of SemiWiki published an article on…Read More

From Space-Central to Space-Time Balanced - A Perspective for Moore’s Law 2.0 and A Holistic Paradigm for EmergenceA friend of SemiWiki published an article on…Read More The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More

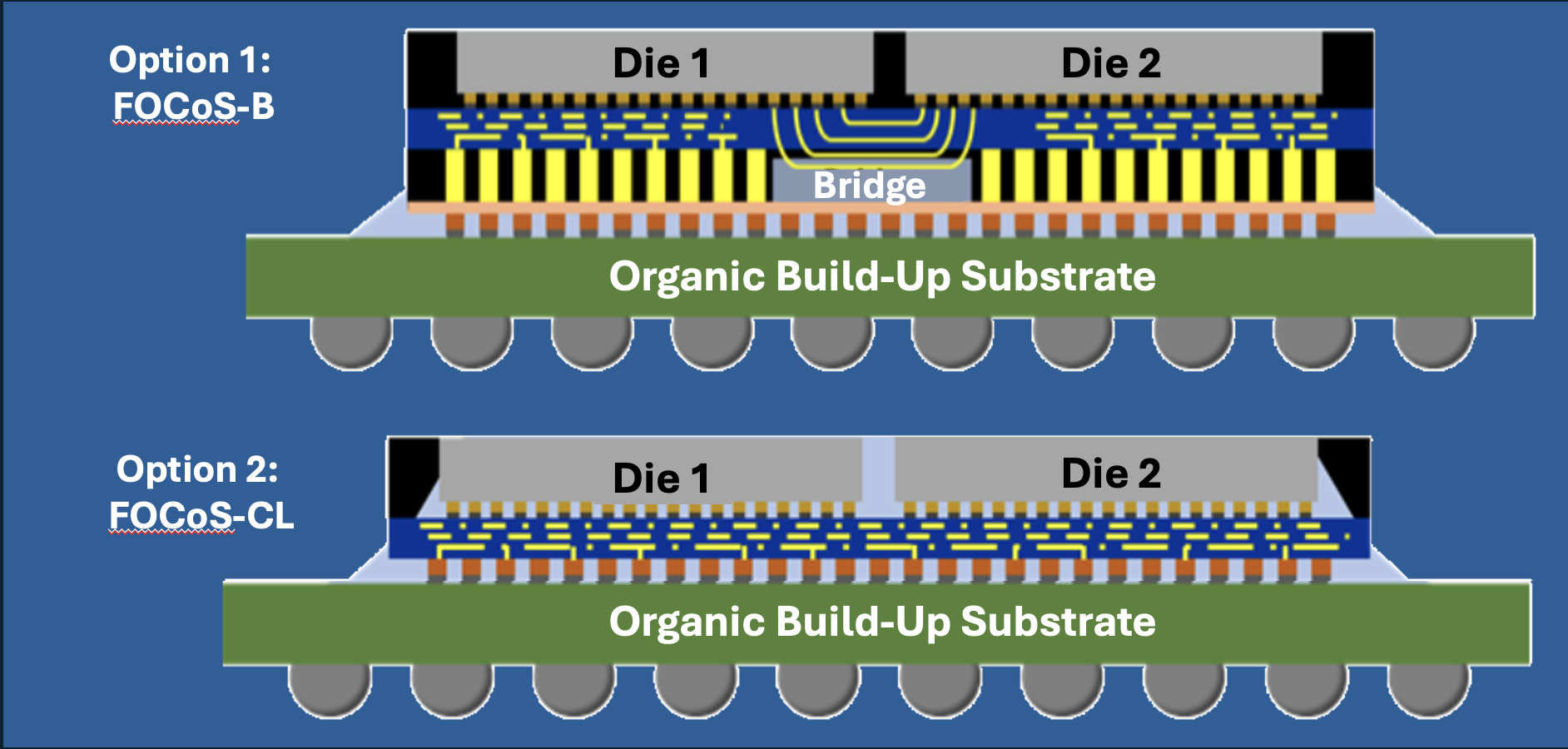

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More

Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More

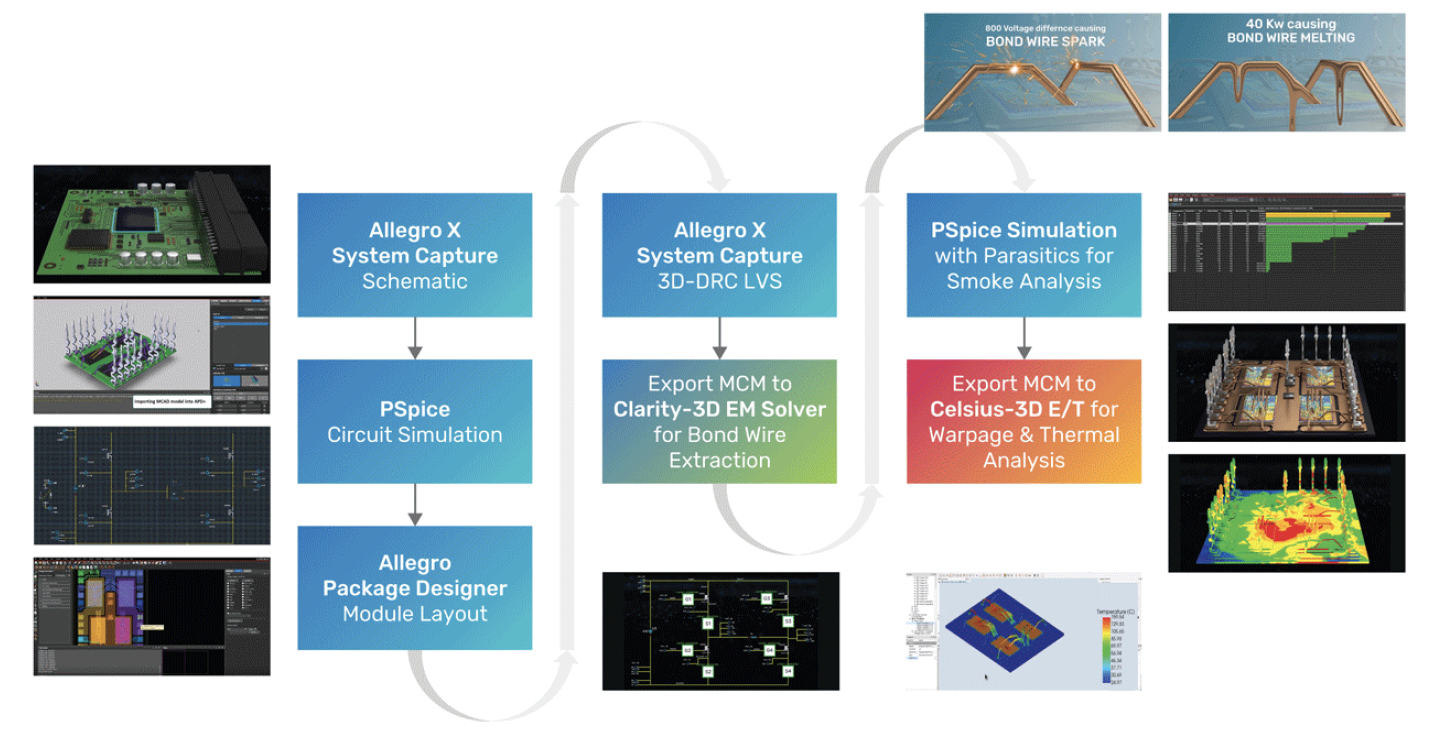

Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read MoreRichard Goering does Q&A with ClioSoft CEO

Richard Goering is well-known from his editorial days at EE Times (going back some 25 years), now at Cadence he blogs at least once a week on EDA topics that touch Cadence tools.

Before DAC he talked with Srinath Anantharaman about how Cadence tools work together with ClioSoft tools to keep IC Design Data Management Simple.

Through… Read More

Intel Briefing: Tri-Gate Technology and Atom SoC

Sorry to disappoint but my 2 hours at the Intel RNB was a very positive experience. It is much more fun writing negative things about industry leaders because I enjoy the resulting hate mail and personal attacks, but the candor and transparency of the Intel guys won me over. They even asked ME questions which was a bit telling. I also… Read More

Webinar: IP integration methodology

The next Apache webinar is coming up on 21st July at 11am Pacific time on “IP integration methodology”.

This webinar will be conducted by Arvind Shanmugavel, Director Applications Engineering at Apache Design Solutions. Mr. Shanmugavel has been with Apache since 2007, supporting the RedHawk and Totem product … Read More

First low-power webinar: Ultra-low-power Methodology

The first of the low power webinars is coming up on July 19th at 11am Pacific time. The webinar will be conducted by Preeti Gupta, Sr. Technical Marketing Manager at Apache Design Solutions. Preeti has 10 years of experience in the exciting world of CMOS power. She has a Masters in Electrical Engineering from Indian Institute of technology,… Read More

And it’s Intel at 22nm but wait, Samsung slips ahead by 2nm…

Another announcement of interest, given all the discussion of Intel’s 22nm process around here, is that Samsung (along with ARM, Cadence and Synopsys) announced that they have taped out a 20nm ARM test-chip (using a Synopsys/Cadence flow).

An interesting wrinkle is that at 32nm and 28nm they used a gate-first process but… Read More

Cadence aquires Azuro

Cadence this morning announced that it has acquired Azuro. Azuro has become a leader in building the clock trees for high performance SoCs. A good rule of thumb is that the clock consumes 30% of the power in an SoC so optimizing it is really important. Terms were not disclosed.

The clock trees involve clock gating which can reduce clock… Read More

On-chip supercomputers, AMBA 4, Coore’s law

At DAC I talked with Mike Dimelow of ARM about the latest upcoming revision to the AMBA bus standards, AMBA 4. The standard gets an upgrade about every 5 years. The original ARM in 1992 ran at 10MIPS with a 20MHz clock. The first AMBA bus was a standard way to link the processor to memories (through the ARM system bus ASB) and to peripherals… Read More

Design for test at RTL

Design for test (DFT) imposes various restrictions on the design so that the test automation tools (automatic test pattern approaches such as scan, as well as built-in self-test approaches) will subsequently be able to generate the test program. For example, different test approaches impose constraints on clock generation… Read More

Intel Twisting ARM?

Intel’s new Tri-Gate technology is causing quite a stir on the stock chat groups. Some have even said if Intel uses its Tri-Gate technology on only Intel processors ARM will be in deep deep trouble. These guys are “Intel Longs” of course and they are battling “Intel Shorts” with cut and paste news clips.

“ARM is in trouble & this… Read More

AI Semiconductor Market