The first thing to realize about Dassault’s Simulation Lifecycle Management platform is that in the non-IC world where Dassault primarily operates, simulation doesn’t just mean functional verification or running Spice. It is anything during the design that produces analytical data. All of that data is important… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

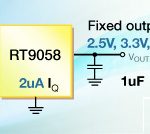

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreDesigning Power Management ICs

With all the focus in design on SoCs in the latest sexy process (Hi-K Metal Gate! FinFETs!) it is easy to forget all the other chips that go into a system. When we say “system on a chip” there are actually very few systems that really get everything onto a single chip. One of the big areas that usually cannot go on the latest… Read More

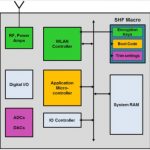

Using OTP Memories To Keep SoC Power Down

Virtually all SoCs require one-time programmable (OTP) memory. Each SoC is different, of course, but two main uses are large memories for holding boot and programming code and small memories for holding encryption keys and trimming parameters, such as radio tuning information and so on.

There are alternatives to putting an OTP… Read More

Who is Blogging at Cadence?

As a blogger in the EDA industry I get to write every week, however I also end up reading every blog on SemiWiki plus multiple other sites to keep current on what’s happening in our business. I thought that it would be informative to look at Cadence Design Systems and how they are using blogging to talk not just about their own EDA… Read More

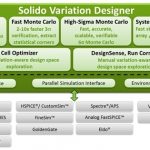

Process Variation is a Yield Killer!

With the insatiable wafer appetites of the fabless semiconductor companies in the mobile space, yield has never been more critical. The result being better EDA tools every year and this blog highlights one of the many examples. It has been a pleasure writing about Solido Design Automation and seeing them succeed amongst the foundries… Read More

Apple’s 64 Bit Plan to Finish Off Android

Many people are underestimating the speed and the magnitude of the transition that is about to take place with the tandem rollout of iOS 7 and the 64 bit A7 processor. While the former provides a nice visual upgrade to the entire ecosystem the latter will be used to collect accolades and drive application development that will result… Read More

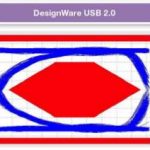

Interface PHY IP supporting Mobile Application on TSMC 20nm? Available!

If we check the many articles daily published in Semiwiki, I am sure that Moore’s Law has been mentioned every single day. There is a good reason why we constantly write about new technologies and advanced features like FinFet, FD-SOI, 450 mm wafers or double patterning: all of these are new challenges that the SC industry will have… Read More

What’s in your network processor?

Recently, one of those very restrained press releases – in this case, Mentor Graphics and Imagination Technologiesextending their partnership for MIPS software support– crossed my desk with about 10% of the story. The 90% of this story I want to focus on is why Mentor is putting energy into this partnership… Read More

Cutting Debug Time of an SoC

The amount of time spent debugging an SoC dwarfs the actual design time, with many engineering teams saying that debug and verification takes about 7X the effort as the actual design work. So any automation to reduce the amount of time spent in debug and verification would directly impact the product schedule in a big way.

An example… Read More

A Brief History of Magillem

Founders

Cyril Spasevski is the President, CTO and founding engineer at Magillem, bringing a team of engineers, all experts with an SoC platform builder tool. In 2006 Cyril and his team met a seasoned business woman, and decided to form Magillem. Design teams were struggling with different tools at different stages of the flow,… Read More

ASML High-NA EUV is Not Ready for High-Volume Production