Increasingly, a GPU is misnamed as a “graphics” processing unit. They are really specialized architecture highly parallel compute engines. You can use these compute engines for graphics, of course, but people are inventive and find ways of using GPUs for other tasks that can take advantage of the highly parallel… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreEarly Test –> Less Expensive, Better Health, Faster Closure

I am talking about the health of electronic and semiconductor design, which if made sound at RTL stage, can set it right for the rest of the design cycle for faster closure and also at lesser cost. Last week was the week of ITC(International Test Conference) for the Semiconductor and EDA community. I was looking forward to what ITC… Read More

Mentor Teaches Us About the Higg’s Boson

Once a year Mentor has a customer appreciation event in Silicon Valley with a guest speaker on some aspect of science. This is silicon valley, after all, so we all have to be geeks. This year it was Dr Sean Carroll from CalTech on The Particle at the End of the Universe, the Hunt for The Higg’s Boson and What’s Next.

Wally … Read More

EDAC Export Seminar: Don’t Know This Stuff…Go Directly to Jail…Do Not Pass Go

I am not making this up: All exports from the United States of EDA software and services are controlled under the Export Administration Regulations, administered by the U.S. Department of Commerce’s Bureau of Industry and Security (BIS). You need to understand these regulations. Failure to comply can result in severe … Read More

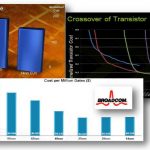

Are 28nm Transistors the Cheapest…Forever?

It is beginning to look as if 28nm transistors, which are the cheapest per million gates compared to any earlier process such as 45nm, may also be the cheapest per million gates compared to any later process such as 20nm.

What we know so far: FinFET seems to be difficult technology because of the 3D structure and so the novel manufacturing… Read More

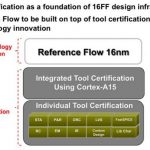

TSMC’s 16FinFET and 3D IC Reference Flows

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd

How to Design an LTE Modem

Designing an LTE modem is an interesting case study in architectural and system level design because it is pretty much on the limit of what is possible in a current process node such as 28nm. I talked to Johannes Stahl of Synopsys about how you would accomplish this with the Synopsys suite of system level tools. He is the first to admit… Read More

Intel Bay Trail Fail

Now that the IDF 2013 euphoria is fading I would like to play devil’s advocate and make a case for why Intel is still not ready to compete in the mobile market. It was very clear from the keynotes that Intel is a chip company, always has been, always will be, and that will not get them the market share they need to be relevant in mobile electronics,… Read More

Semiconductor Manufacturing in India?

Last week I heard about the Indian Cabinet approving the proposal for setting up of two Fabs in India. One led by IBM, Tower Jazzand JP Associates(an Indian business house), and the other led by HSMC(Hindustan Semiconductor Manufacturing Co.), ST Microelectronicsand Silterra. Indian Semiconductor community including IESA… Read More

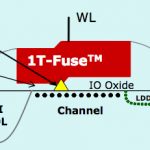

Sidense and TSMC Processes

I’ve written before about the basic capabilities of Sidense’s single transistor one-time programmable memory products (1T-OTP). Just to summarize, it is an anti-fuse device that works by permanently rupturing the gate oxide under the bit-cells storage transistor, something that is obviously irreversible.… Read More

Solving the EDA tool fragmentation crisis