In the spring of 1984, Mark Flomenhoft, Ph.D., approached Aki Fujimura, Randy Smith, and Steve Teig, to join him in developing a business plan to create a new EDA place and route (P&R) company. The three young software engineers all worked at Trilogy Systems Corporation where Mark was a director in the design automation department.… Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

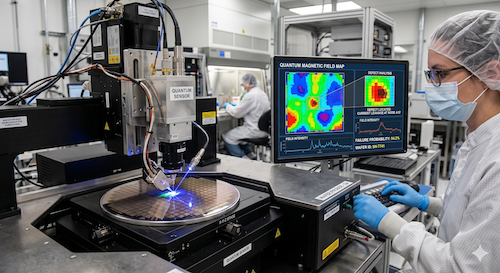

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More

Sensing. A Quantum Tech Ready for Market?While the quantum world revolves around quantum computing,…Read More #DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read More

#DAC2026 Marks Another Pivotal Moment for the Semiconductor IndustryThe 2026 Design Automation Conference (DAC 2026) marks…Read MoreWhat Can Accelerate 3D Semiconductor Manufacturing?

In the beginning of this decade there was a lot of buzz around 3D chip manufacturing. Many EDA tools were developed to facilitate semiconductor designs in 3D space. Naturally, we are moving to the edge on 2D without much room to further squeeze transistors and interconnect. However, lately I haven’t heard much about 3D products.… Read More

Mobile-Ready EDA and Semi IP Web Sites

18 months ago I blogged about how the mobile revolution that we enjoy today is really enabled by EDA software and IP in the hands of SoC designers, yet very few EDA and Semi IP companies had mobile-ready web sites. In that past 18 months we’ve witnessed only a handful of companies migrate to mobile-friendly web sites, the most… Read More

Managing All of That IP on Your SoC

It’s common to see an SoC with a few hundred IP blocks today, which is quite a change from full-custom IC designs developed in the early days (i.e. 1980’s) where there was little IP re-use at all. This shift in the technology and business of IP has created a relatively new industry of IP providers from small to large in size.… Read More

What do Intel and Congress Have in Common?

The war of words continues, when will it end? I consider myself a reasonably educated and informed person, certainly above average by U.S. standards, yet I have no idea why the U.S. Government continues to write checks they cannot cash and I don’t know who to believe in the resulting media blasts. I truly miss the days of Ross… Read More

Catch Mentor’s embedded sessions at ARM TechCon

For Halloween this year, why not tell your embedded software debug horror stories at ARM TechCon? Mentor will have several campfire sessions you should consider attending, but here my Halloween thread breaks down. These three sessions are all quite cheery.

This one, Software Debug on ARM Processors in Emulationis on using emulation… Read More

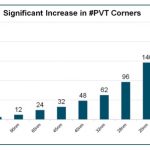

Spectre from Cadence Goes FastSPICE

Transistor-level circuit designers have an insatiable appetite to run numerous SPICE circuit simulations in order to determine circuit speed, current and power across Process, Voltage and Temperature (PVT) conditions. Just look at the number of PVT corners increasing as the technology nodes go to 16nm:

The good news today … Read More

Managing Multi-site Design with Cliosoft at LBNL

With the award of the Nobel prize for physics to Higgs (who used to work in the same building at Edinburgh as I did, reflected glory) and Englert yesterday, CERN has been in the news. ClioSoft has an interesting presentation given at CERN about designing a detector chips. The work was done two or three years ago, managed from Lawrence… Read More

Can you Publicly Benchmark EDA Tools?

There is an interesting discussion on SemiWiki in regards to the age old question aboutbenchmarking EDA tools. I remember benchmark discussions at my first DAC in 1984. It was deemed impossible to do a “fair” public benchmark then and it’s not possible now, just my opinion of course but let me tell you why. Simply stated it is a legal,… Read More

Mentor Seminar: Evolution of diagnosis-driven yield analysis

It’s a fact that new process nodes come with some amount of yield challenges. One way to find and eliminate silicon defects is through diagnosis-driven yield analysis (DDYA), which is the topic of a free seminar by Mentor Graphics in Fremont this Thursday, October 10 from 11:30am – 2pm (yes, lunch is included because Mentor… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior