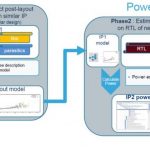

It was an interesting webinar I attended, presented by STMicroelectronicson how they are benefited in power saving and thermal dissipation by using FDSOI technology and also by using PowerArtist in their design. So, it’s an advantage from both sides – semiconductor technology and semiconductor design tool. It’s worth attending… Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read MoreStick to the script for repeatable FPGA-based prototyping

70% of today’s ASIC and SoC designs are being prototyped on FPGAs. Everybody knows that. But, did you know that automating the process of converting what could be thousands of ASIC “golden” files into FPGA-friendly versions can mean big savings in a large design?… Read More

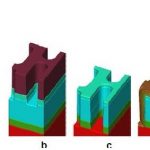

How to Quickly Optimize BEOL Process at Your Desk?

Engineers are always looking to improve the efficiency of how they work, but don’t want to sacrifice accuracy in the process. This is true in the world of semiconductor process development, where traditional build-and-test cycles are both time and resource intensive. But what if there was a way to do certain steps in a ‘virtual’… Read More

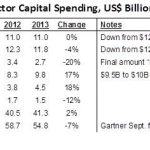

Another Negative Year for Semiconductor CapEx

Global semiconductor capital spending is headed for another decline in 2013, following a 12% decline in 2012. Gartner’s September forecast called for a 7% decline in 2013. Most of the major spenders expect flat to declining expenditures in 2013. Intel in July estimated 2013 spending of $11 billion, flat with 2012 and down from … Read More

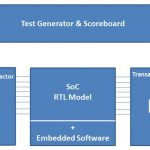

With SCE-MI, timing really is everything

In one of my favorite movies, Brad Pitt utters the only question that matters in baseball or technology management in the face of uncertainty: “Okay, good. What’s the problem?” Not surprisingly in that scene, as the question circles the table of experts used to doing things the old way, not a single one can answer it correctly in the… Read More

TSMC Open Innovation Platform Forum, October 1st

One of TSMC’s two big Silicon Valley events each year is the Open Innovation Platform (OIP) Forum. This year it is on Tuesday October 1st. It is in the San Jose Convention Center and starts at 9am (registration opens at 8am). Pre-registration to attend is now open here or click on the image to the right.

From 9.10 to 9.40 is the … Read More

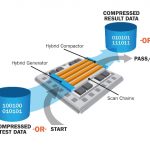

What Mentor Said at ITC

At the ITC test conference in early September, Mentor made three announcements. ITC is a big event for Mentor’s test group, and where they usually roll out their new tools and capabilities. The indefatigable Steve Pateras was captured on film describing them.

I’ve summarize Mentor’s three announcements and added… Read More

The US Executive Forum 2013

The US Executive Forum hosted by the Global Semiconductor Alliance was held last night at the beautiful Rosewood Sand Hill Hotel in Menlo Park. We all have memorable events in our professional lives and this is one of mine, absolutely. The audience was filled with semiconductor executives from around the world who chatted freely… Read More

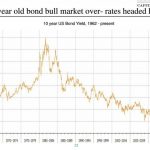

Dan Niles: Tapering and the Global Economy

Yesterday was Dan Niles quarterly review that he does for GSA. As always he starts from the big picture of the world economy and works his way to a semiconductor forecast. The focus of this quarter was whether the world economy is strong enough for the US to “taper” and reduce the amount of quantitative easing (aka flooding… Read More

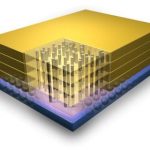

Hybrid Memory Cube Shipping

Today Micron announced that it is shipping 2GB Hybrid Memory Cube (HMC) samples. The HMC is actually 5 stacked die connected with through-silicon-vias (TSVs). The bottom die is a logic chip and is actually manufactured for Micron in an IBM 32nm process (and doesn’t have any TSVs). The other 4 die are 4Gb DRAM die manufactured… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era