If you ask to IP vendors selling functions, PHY or Controller, supporting Interface based protocols which part is the master piece, the controller IP only vendors will answer: certainly my digital block, look how complex it has to be to support the transport and logical part of the protocol! Just think about the PCI Express gen-3… Read More

CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read More

CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read More Rethink Scoreboards to Supercharge AI-Era CPUsBy Dr. Thang Minh Tran, CEO/CTO Simplex Micro…Read More

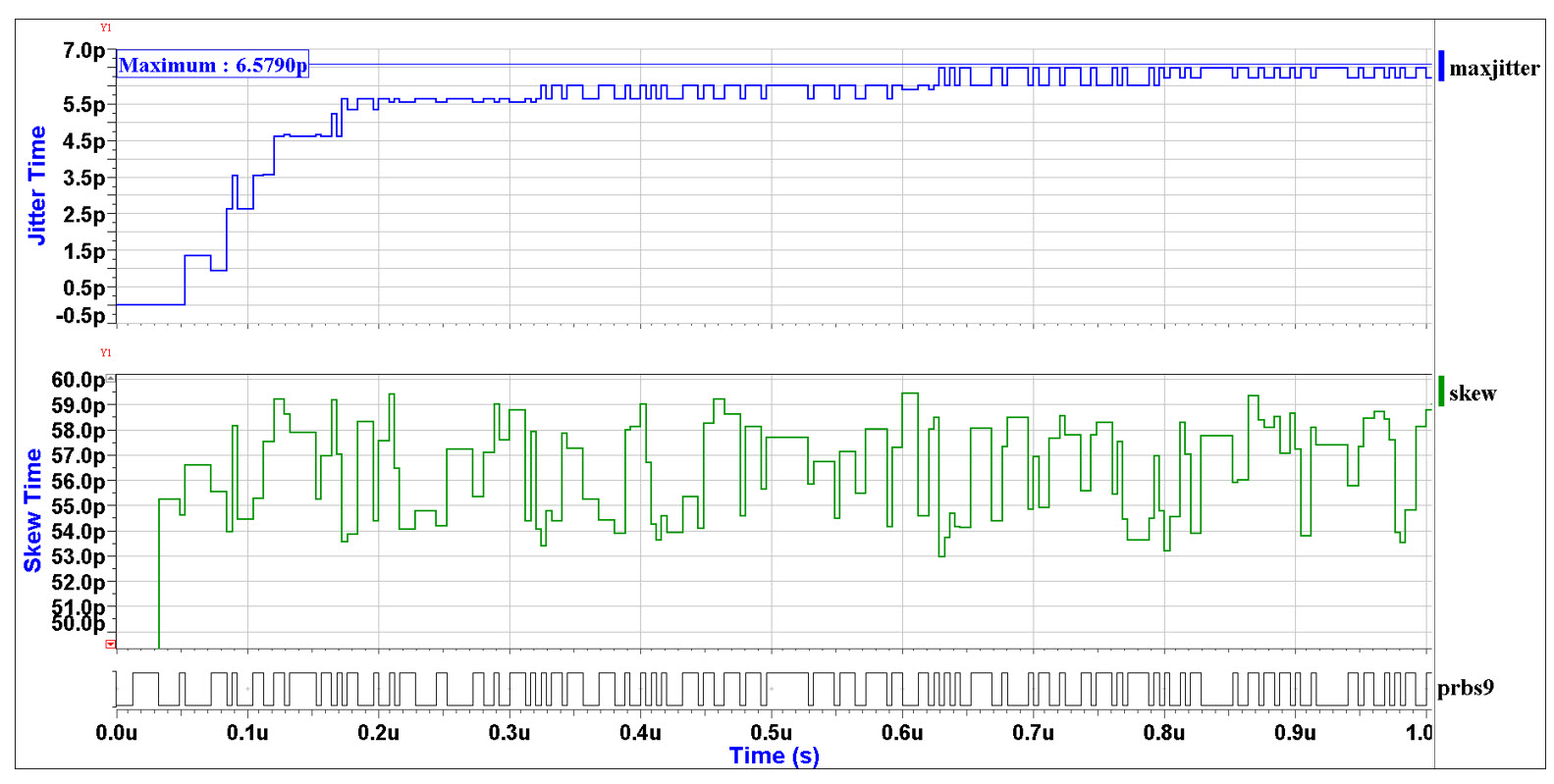

Rethink Scoreboards to Supercharge AI-Era CPUsBy Dr. Thang Minh Tran, CEO/CTO Simplex Micro…Read More Jitter: The Overlooked PDN Quality MetricBruce Caryl is a Product Specialist with Siemens EDA…Read More

Jitter: The Overlooked PDN Quality MetricBruce Caryl is a Product Specialist with Siemens EDA…Read More CEO Interview with Vamshi Kothur, of Tuple TechnologiesIt was my pleasure to meet with Vamshi…Read More

CEO Interview with Vamshi Kothur, of Tuple TechnologiesIt was my pleasure to meet with Vamshi…Read More Webinar – Power is the New Performance: Scaling Power & Performance for Next Generation SoCsWhat if you could reduce power and extend…Read More

Webinar – Power is the New Performance: Scaling Power & Performance for Next Generation SoCsWhat if you could reduce power and extend…Read MorePhil Kaufman Award Recipient 2013: Chenming Hu

This year’s recipient of the Kaufman Award is Dr Chenming Hu. I can’t think of a more deserving recipient. He is the father of the FinFET transistor which is clearly the most revolutionary thing to come along in semiconductor for a long time. Of course he wasn’t working alone but he was the leader of the team at UC… Read More

TSMC to Talk About 10nm at Symposium Next Week

Given the compressed time between 20nm and 16nm, twelve months versus the industry average twenty four months, it is time to start talking about 10nm, absolutely. Next Tuesday is the 19th annual TSMC Technology Symposium keynoted of course by the Chairman, Dr. Morris Chang.

Join the 2013 TSMC Technology Symposium. Get the latest… Read More

Intelligent tools for complex low power verification

The burgeoning need of high density of electronic content on a single chip, thereby necessitating critical PPA (Power, Performance, Area) optimization, has pushed the technology node below 0.1 micron where static power becomes equally relevant as dynamic power. Moreover, multiple power rails run through the circuit at different… Read More

What really means high reliability for OTP NVM?

Normal operation range for a Semiconductor device is not made equal for systems… If you consider a CPU running inside an aircraft engine control system, this device should operate at temperature ranged between -55°C and +125°C, when an Application Processor for smartphone is only required to operate in the 0°C to +70°C range. … Read More

TSMC Tapes Out First 64-bit ARM

TSMC announced today that together with ARM they have taped out the first ARM Cortex-A57 64-bit processor on TSMC’s 16nm FinFET technology. The two companies cooperated in the implementation from RTL to tape-out over six months using ARM physical IP, TSMC memory macros, and a commercial 16nm FinFET tool chain enabled by… Read More

GF, Analog and Singapore

The world is analog and despite enormous SoCs in the most leading-edge process node being the most glamorous segment of the semiconductor industry, it turns out that one of the fastest growing segments is actually analog and power chips in older process technologies. Overall, according to Semico, analog and power ICs, including… Read More

April 17-19: Overbooked!

For three days in a couple of weeks time there is a crash of conferences, spread out all over the extended Bay Area.

Firstly, from 17-19th April at the Santa Clara Hyatt is the Linley Mobile Conference. This covers all things microprocessor in the mobile industry. Details of the conference including the full agenda are here. The conference… Read More

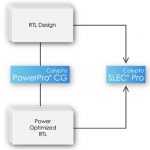

Clock Gating: Sequential Is Better

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential… Read More

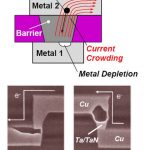

Power integrity: ground, and other fairy tales

Ground. It’s that little downward-pointing triangle that somehow works miracles on every schematic. It looks very simple until one has to tackle modern power distribution network (PDN) design on a board with high speed and high power draw components, and you soon discover ground is a complicated fairy tale with a lot of influences.… Read More

Facing the Quantum Nature of EUV Lithography