On April 18, 2014 in Monterey California there will be a series of discussions on the challenges of IP reuse. These discussions are part of the 2014 Electronic Design Process Symposium (EDPS). Representatives from IP, ASIC, foundry and EDA will weigh in the challenges and issues. Here is a preview of one of the presentations from… Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More

When a Platform Provider Becomes a Competitor: Why Arm’s Silicon Strategy Changes the IncentivesMarc Evans, Director of Business Development & Marketing,…Read More yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More

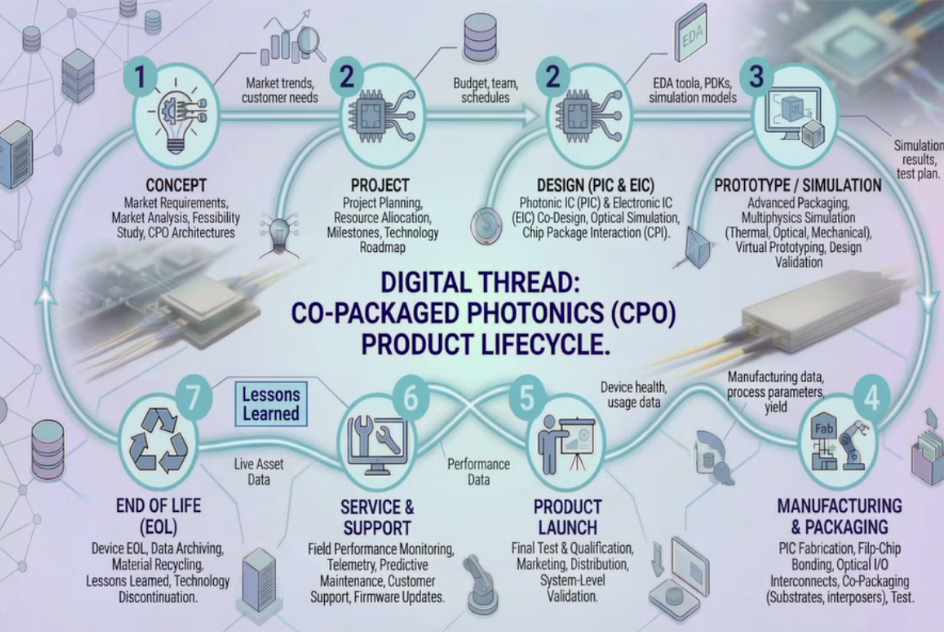

yieldWerx Delivers a Master Class in Co-Packaged Photonics ImplementationWe all know the semiconductor industry is seeing…Read More RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More

RISC-V Has Momentum. The Real Question Is Who Can DeliverRISC-V has momentum. The industry knows it. The…Read More Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read MoreJasper Announces Sequential Equivalence Checking

Jasper finally announced their sequential equivalence checking app this morning. I say finally because they haven’t really tried to keep it a secret. They talked about it at the end of last year the Jasper User Group meeting and it has even had a page on their website. But formally the product was announced today.

The new JasperGold… Read More

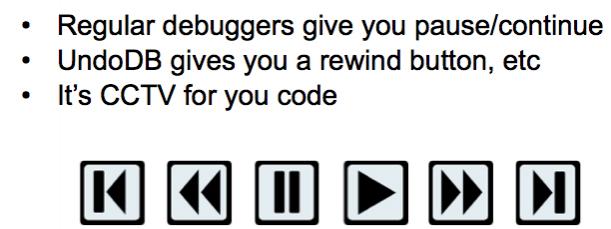

Undo Your Code

When I was a Virtutech a few years ago we had a product called Hindsight. It looked close to magic when you used it since it allowed you to run code backwards. I assume that the technology is still lurking under the hood in Wind River’s Simics product, now part of Intel. The way the code worked is that as the software executed, Simics… Read More

Bye-Bye DDRn Protocol?

In fact, this assertion is provocative, as the DDR4 protocol standard has just been released by JEDEC… after 10 years discussion around the protocol features. Yes, the first discussions about DDR4 have started ten years ago! Will DDR4 be used in the industry? The answer is certainly yes, and DDR4 will most probably be used for years.… Read More

Bluetooth Smart radio IP, backed by ARM

For most devices, the on ramp to the Internet of Things means wireless, connecting a microcontroller or SoC via some kind of radio. It seems every merchant semiconductor company and embedded software firm has jumped on board the IoT wagon. There is a litany of chips, modules, operating systems, and protocol stacks already, and … Read More

Care and trimming of MEMS sensors

My first job in electronic design circa 1981 was making analog autopilots and control devices for RPVs – the early form of what today we call UAVs. A couple of really delicate boxes with gyroscopes, accelerometers, and magnetometers, and several boards full of LM148 quad op-amps surrounded by a lot of resistors and capacitors made… Read More

Social Media at Atrenta

Atrentais well-known for their SpyGlass software that enables SoC engineers to run early design analysis on RTL code and create a hardware virtual prototype for analysis prior to implementation. Visiting their website you quickly see that social media plays an important role in connecting with engineers as links for Facebook,… Read More

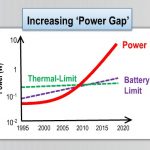

Applied Power Electronics Conference & Exposition 2014: "Less Power"

On the television show “Home Improvement”, Tim Allen’s character always sought “more power” for whatever project he was working on. The theme of the Applied Power Electronics Conference and Exposition (APEC) 2014 could have been “less power”. APEC 2014 featured five days of seminars and sessions including professional education,… Read More

IP Challenges, FinFET, 3D-IC, and FD-SOI Updates

Semiwiki is proud to be a sponsor of EDPS 2014:

April 17 & 18, 2014

Monterey Beach Hotel, Monterey, CA

Sponsored by:

IEEE Computer Society of Silicon Valley (CS-SCV)

IEEE Computer Society

Design Automation Technical Committee (DATC)

Council on Electronic Design Automation (CEDA)

The Electronic Design Processes Symposium… Read More

Early RTL Power Analysis and Reduction

Power analysis and reduction for SoC designs is a popular topic because of our consumer electronics dominated economy, and the need to operate devices on a battery source for the maximum time before a recharge. Just from my desk I can see multiple battery-powered devices: Laptop, tablet, smart phone, e-book reader, bluetooth … Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea