Cadence is excited to bring a full slate of demos, technical presentations, papers, and more to the Design Automation Conference (DAC) June 1-5, 2014, in San Francisco, CA. From our technical experts, you’ll learn tips and techniques from areas including low power, mixed signal, advanced nodes, signoff, verification, and IP,… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreTaming The Challenges of SoC Testability

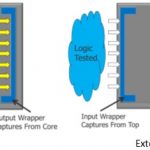

With the advent of large SoCs in semiconductor design space, verification of SoCs has become extremely challenging; no single approach works. And when the size of an SoC can grow to billions of gates, the traditional methods of testability of chips may no longer remain viable considering the needs of large ATPG, memory footprint,… Read More

A Brief History of the Apple MacBook Pro

I’m typing this blog today with my trusty Apple MacBook Pro – a 17″ laptop with matte display and 16GB of RAM, but don’t stereotype me as an Apple fanboy because I also own the fantastic Samsung Galaxy Note II phone (aka phablet). Some industry pundits would have us believe that desktops and laptops are going… Read More

A Brief History of MunEDA

In 2002, MunEDA was launched under the guidance of EDA academic veterans and IEEE fellows Prof. Kurt Antreich and Prof. Helmut Gräb (TUM Munich Technical University ) which represented 20 plus years of EDA research and experience. All MunEDA tools are combined in a tool suite called WiCkeD[SUP]TM[/SUP]. The tool suite brand was… Read More

Teach Yourself Silvaco

In the dim and distant past, if you wanted to learn how to use a particular EDA tool then you would go on a training course. This would often be multiple days and often a significant dollar investment too. For most EDA companies, that option still exists and the big 3 have quite extensive training catalogs.

But nowadays it is often easier… Read More

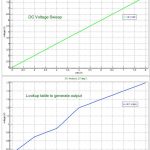

Solido Patent Enabling Variation-Aware Custom IC Design

This is patent number twelve for Solido Design Automation THE leading provider of variation analysis and design software for high yield and performance IP and system-on-chip (SOCs). Additional patents are pending on high-sigma analysis, high-dimensional data mining, and other technologies to design and verify custom integrated… Read More

New Frontiers in MEMS and Their Enablers

With the 51[SUP]st[/SUP] DACapproaching quickly, I spent some time last week-end to look around about what new trends, technologies and innovations will be most talked about during DAC. Every year, I find some exciting new technologies in the semiconductor industry and the overall semiconductor ecosystem that get wider exposure… Read More

Healthy Semiconductor Growth in 2014 and 2015

The first quarter 2014 semiconductor market was $78.5 billion, down 1.8% from fourth quarter 2013 and up 11.4% from a year ago, according to World Semiconductor Trade Statistics (WSTS). The year-to-year growth was the highest since 4Q 2010. The year-to-year growth has been accelerating for the last four quarters. Our February… Read More

Is the Chief IoT Barrier Privacy?

The World Affairs Council event, The Internet of Things: Global Implications of Merging the Physical and Digital Worlds, was hosted by Cadence last week. One thing I can tell you is that Cadence sure does know how to throw a party! They had me at free food and beer but the topic was also of great interest since my next project will involve… Read More

Mentor @ #51DAC Must See!

We’ve packed each day full of exciting activities focused on the latest in cutting-edge design. Use this site to find your favorite Mentor experts and events—whether in our suites and networking events, at our partner booths or in the conference. You won’t want to miss a thing!

Celebrating Your Design Creativity!

Rejuvenate with… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center